## processor handbook

04/34/45/55/60

## processor handbook

04/34/45/55/60

## digital

digital equipment corporation

## Copyright © 1978, by Digital Equipment Corporation

PDP, UNIBUS are registered trademarks of Digital Equipment Corporation

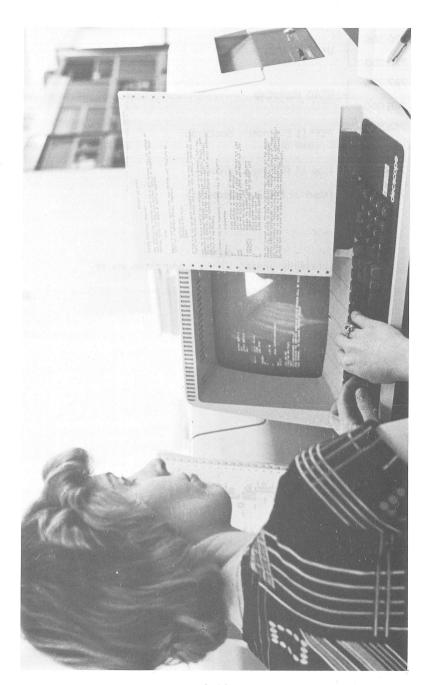

This handbook was designed, produced and typeset by DIGITAL's Sales Support Literature Group using an in-house text-processing system operating on a DECSYSTEM-20.

## **CONTENTS**

| CHAPTER 1  | INTRODUCTION                  |

|------------|-------------------------------|

| CHAPTER 2  | UNIBUS                        |

| CHAPTER 3  | ADDRESSING MODES 21           |

| CHAPTER 4  | INSTRUCTION SET 41            |

| CHAPTER 5  | PROGRAMMING TECHNIQUES 85     |

| CHAPTER 6  | PDP-11/04, PDP-11/34 129      |

| CHAPTER 7  | PDP-11/45, PDP-11/55 159      |

| CHAPTER 8  | PDP-11/60 199                 |

| CHAPTER 9  | MICROPROGRAMMING 233          |

| CHAPTER 10 | FLOATING POINT PROCESSORS 247 |

| APPENDIX A | UNIBUS ADDRESSES A-           |

| APPENDIX B | INSTRUCTION SET TIMING B-     |

| INDEX      | Index-                        |

## **CHAPTER 1**

## INTRODUCTION

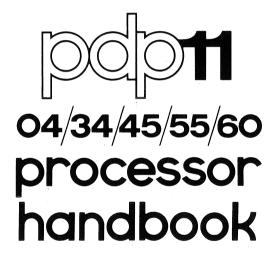

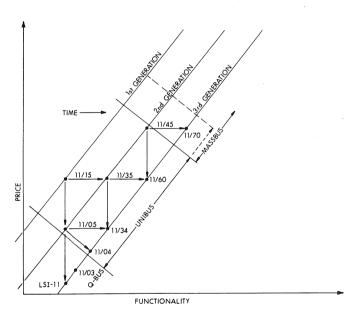

DIGITAL's 11 family of interactive computers ranges in size from the single-board LSI-11 through the extensive PDP-11 group. Development efforts are constantly expanding both ends of the spectrum as well as creating enhanced products in the PDP-11 price versus performance matrix.

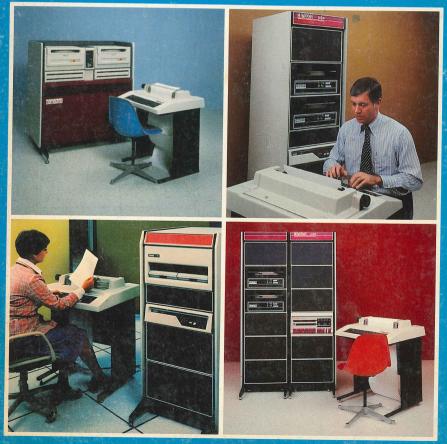

Figure 1-1 PDP-11 Family Development

The processors specifically discussed in this handbook are the:

- ●PDP-11/04

- ●PDP-11/34

- PDP-11/45

- ●PDP-11/55

- ●PDP-11/60

### INTRODUCTION

PDP is the acronym for Programmable Data Processor; 11 is the number of the series of the processors designed by DIGITAL. The numeral following the 11 refers to the *general* relative power of the processor. The PDP-11/60 is, for example, a more powerful processor than the PDP-11/04.

Historically, there were PDP-1s through PDP-10s designed before the PDP-11 family appeared. Although the PDP-8 family continues to be one of DIGITAL's most successful and stable product lines, it is in the PDP-11 family that there has been the greatest range of growth and development. PDP-11 processors are a family based on common architecture. Compatibility is inherent in design, and is reflected in the software and in the peripheral options.

It is possible, for example, to develop programs on the smallest PDP-11 family member, the PDP-11/03, and, with only slight modifications, run them on any other PDP-11 system. Peripherals such as video terminals and line printers are equally upward and downward compatible in their ability to interface with PDP-11 family members.

The processors which are discussed specifically in this book have one outstanding characteristic in common: they all process data on a data bus called the UNIBUS.

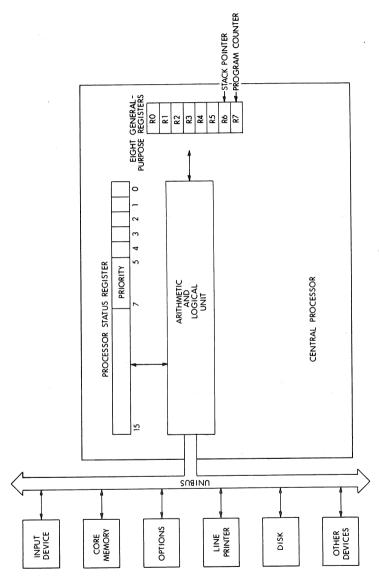

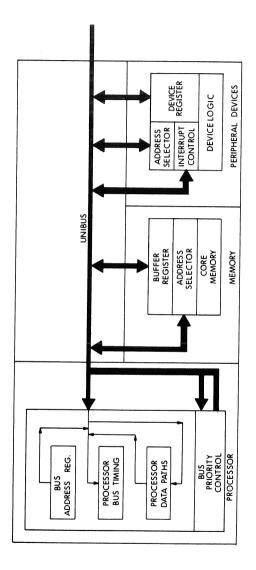

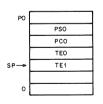

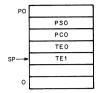

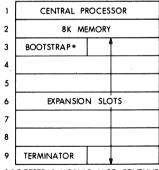

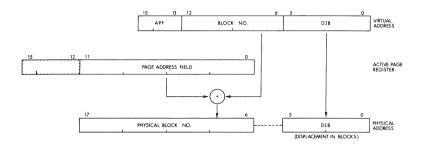

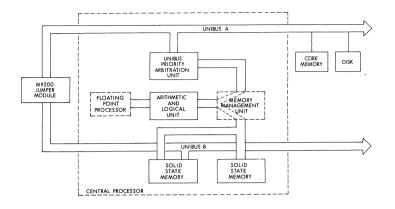

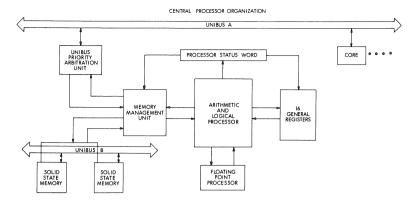

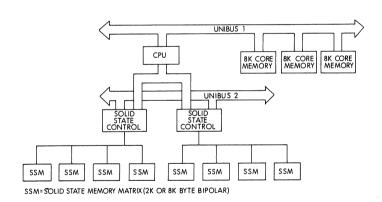

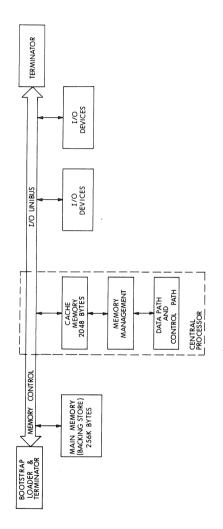

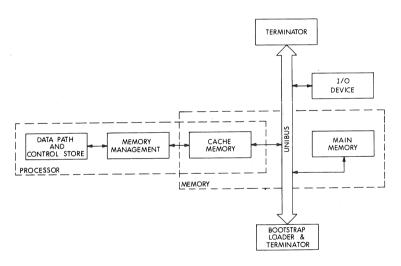

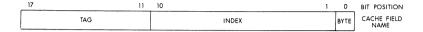

The UNIBUS (discussed in detail in Chapter 2) was first announced by DIGITAL in 1970, in conjunction with the announcement of the first PDP-11, the PDP-11/20. It is the UNIBUS and its unique capabilities which have provided the flexibility and growth options for the PDP-11 family members discussed in this handbook. Figure 1-2 illustrates the block structure of the PDP-11.

Beyond the UNIBUS commonality, each PDP-11 processor has features and capabilities uniquely suited for various applications. Some functionally similar features have been accomplished with different implementations, therefore, there is some repetition of information in the chapters describing the individual processor members of the PDP-11 family, especially in areas like memory management. It is often necessary to discuss each separately because what may appear to be very subtle differences in operations may actually be key to a certain processor's uniqueness.

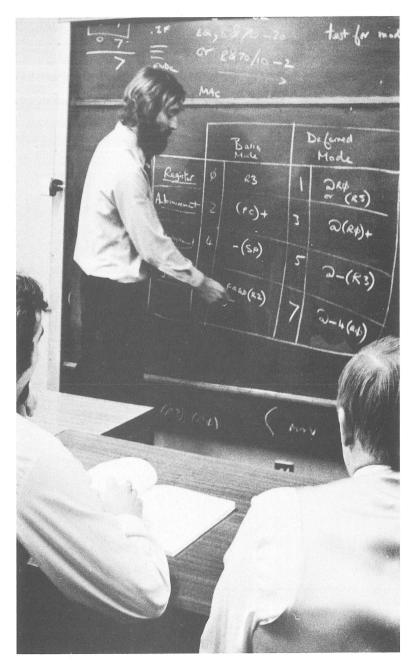

## PROGRAMMING THE PDP-11

Information is provided in this handbook about the assembly language parameters, processes, and techniques involved in programming the PDP-11. DIGITAL publishes tutorial software documentation that provides detailed information about using the PDP-11 instruction set to develop programs. There are also well-developed courses for customers given by DIGITAL's Education Services group.

Figure 1-2 PDP-11 Block Structure

## INTRODUCTION

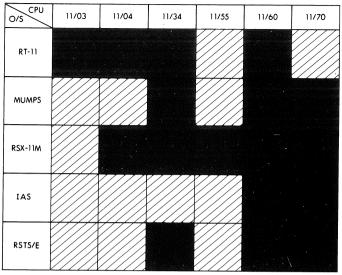

The material presented on the PDP-11 instruction set, addressing modes, and on programming techniques is intended, with the examples included, to illustrate the range of and possibilities for program development. A companion book, the PDP-11 Software Handbook, clearly explains the operating systems and associated software which run on the PDP-11 family of processors. Table 1-1 illustrates these software products.

Table 1-2 PDP-11 Software Systems Summary

| LSI-11 based                                                                                                                                    | 11/04                                                                                                                                        | 11/34                                                                                                                            | 11/55                                                                                                                                               | 11/60                                                                                                            | 11/70                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 16K to 56K byt<br>subset MACRO<br>bytes: Foregrot<br>support string of<br>CRO assembler<br>ing as many as<br>as 8 users in 48<br>under F/B moni | ACRO included; F                                                                                                                             | n 16K bytes: Sin<br>FORTRAN IV, F<br>(F/B) or SJ op<br>atory and graph<br>user BASIC avai<br>J monitor). MU E<br>monitor; and as | ngle Job (SJ) op<br>OCAL as options<br>peration; langua-<br>ics peripherals;<br>lable as option s<br>BASIC supports is<br>s many as 4 in 56         | peration;<br>s. In 32K<br>ges can<br>full MA-<br>support-<br>as many<br>6K bytes                                 |                                                                                                        |

|                                                                                                                                                 | MUMPS-11 Multi<br>56K to 248K byte<br>are needed to su<br>simultaneously (c<br>Languages:MUM                                                 | s of memory. A 5<br>pport 6 users. S<br>lepending on pr                                                                          | 56K system supp<br>upports maximu                                                                                                                   | orts 2-4 users. A                                                                                                | t least 64K bytes<br>ing users, 30-40                                                                  |

| -                                                                                                                                               | 96<br>De<br>po<br><b>La</b>                                                                                                                  | K to 248K bytes<br>pending on dis<br>rt a maximum of                                                                             | C-PLUS included                                                                                                                                     | 256K to 4096K configuration, RS                                                                                  | STS/E can sup-                                                                                         |

| 16K to 248K of a bytes required FORTRAN.                                                                                                        | te-only Real-Time<br>memory. 8K (byte<br>for on-line task l<br>gram developme                                                                | es) system allow<br>loading or supp                                                                                              | s 4K for user tas<br>port for tasks wi                                                                                                              | ritten in                                                                                                        |                                                                                                        |

|                                                                                                                                                 | RSX-11M Small-t<br>32K to 248K bytes<br>allows up to 8K for<br>required for full M<br>tion tasks executing<br>Languages: MAC<br>are options. | s of memory or 2<br>or user tasks; inc<br>MACRO support<br>on, or memory n                                                       | 56K to 4C96K by<br>cludes a subset o<br>, concurrent pro<br>nanagement sup                                                                          | tes on 11/70. 16h<br>of MACRO. At lea<br>gram developme<br>port. Error loggir                                    | K (bytes) system<br>st 48K bytes are<br>ent and applica-<br>ng supported.                              |

|                                                                                                                                                 |                                                                                                                                              | by joil tio co be int po La                                                                                                      | S Multi-purpose 8K to 248 K byte tes on 11/70. Ti o processing wit on sexecution. D offiguration, as on eractive users o orted. GRTRAN IV-PLUS ons. | es of memory or meshared interach concurrent recepending on dispending on the an 11/60; as on an 11/70. Errocket | 256K to 4096K ctive and batch al-time applicask and memory active users can many as 20 or logging sup- |

## PERIPHERALS

DIGITAL manufactures a full range of peripheral equipment designed to meet specific needs as well as to maintain PDP-11 family compatibility. I/O and storage devices range from paper tape readers through high volume disk packs and from the DECwriter to the intelligent terminals which provide both hard copy and video display. There is a complete spectrum of peripheral devices available to complement the software, to provide the complete answer to customer needs in all product line areas — business, education, industry, laboratory, and medicine.

The Peripherals Handbook and the Terminals and Communications Handbook describe in detail the optional equipment available for use with the PDP-11 family members.

## SPECIALIZED SYSTEMS

DIGITAL's Computer Special Systems (CSS) and OEM (Original Equipment Manufacturers) groups can provide the exact hardware and software combination to fill any customer need. Software Services provides software consultation services for customers who have specialized applications software needs.

## **PACKAGE SYSTEMS**

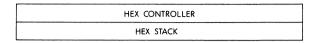

DIGITAL's Package Systems program offers you the opportunity to purchase a well-defined, pretested, hardware/software system, rather than purchasing the options separately. Package systems are fully equipped PDP-11 configurations including operating system, bootstrap loader, clock, expander boxes, cabinets, and all required cables. Entry level systems consist of the correct minimum set of options defined in the Software Product Description (SPD) as necessary to run the operating system. Medium and high performance systems have expanded configurations that in some cases substantially exceed minimum SPD requirements. Package systems are available for all of DIGITAL's major operating systems. The introductory family of systems represents the combined effort of the product lines and of central engineering to offer the best set of systems to meet customer application needs. Package systems are priced less than the sum of the individual options. Figure 1-3 illustrates the combinations (shaded portions) of options currently available under the Package Systems program. For example, all the operating systems listed are available as a package system with the PDP-11/60 processor.

## INTRODUCTION

## PDP-11 FAMILY PACKAGE SYSTEMS

Figure 1-3 Package Systems

## **DOCUMENTATION**

DIGITAL offers several levels of technical documentation describing PDP-11 software and hardware. The PDP-11 Handbook series, which includes the Peripherals Handbook, the Terminals and Communications Handbook, and the Software Handbook, presents an introductory technical level of PDP-11 family information. The hardware user documentation and software tutorial documentation which accompany the delivery of a PDP-11 computer system offer the most detailed levels of information. There are also several good books published by commercial publishers which discuss the PDP-11 family. Specific topics like microprogramming are also well-covered in commercially available books. If you have a specific documentation need, discuss the issue with a DIGITAL salesperson, who will guide you to the appropriate literature.

## NUMERICAL NOTATION

Three number systems are used in this handbook: octal, base eight; binary, base two; and decimal, base ten. **Octal** is used for address locations, contents of addresses, and instruction operation codes. **Binary** is used for descriptions of words and **decimal** for normal quantitative references.

## **CHAPTER 2**

## UNIBUS

The UNIBUS is the outstanding design feature that makes possible the strengths and flexibility of the PDP-11 family members discussed in this book. DIGITAL's unique data bus, the UNIBUS, provides the hardware and software backbone of the PDP-11/04, 34, 45, 55, and 60 processors. The UNIBUS was the first data bus in the history of the minicomputer industry to enable devices to send, receive, or exchange data without processor intervention and without intermediate buffering in memory.

## PDP-11 ARCHITECTURE AND THE UNIBUS

PDP-11 architecture takes advantage of the UNIBUS in its method of addressing periperal devices. Memory elements, such as the main core memory or any read-only or solid state memories, have ascending addresses starting at zero, while registers that store I/O data or the status of individual peripheral devices have addresses in the highest 4K words of addressing space.

There are tens of thousands of memory addresses, but only two — one for data, one for control — for some peripheral devices, and up to half a dozen for more complicated equipment like magnetic tapes or disks.

The PDP-11 UNIBUS consists of 56 signal lines, to which all devices, including the processor, are connected in parallel.

51 lines are bidirectional and five are unidirectional.

Communication between any two devices on the bus is in a master/slave relationship. During any bus operation, one device, the bus master, controls the bus when communicating with another device on the bus, called the slave. For example, the processor, as master, can fetch an instruction from the memory, which is always a slave; or the disk, as master, can transfer data to the memory, as slave. Master/slave relationships are dynamic: the processor, for example, may pass bus control to a disk, then the disk may become master and communicate with slave memory.

When two or more devices try to obtain control of the bus at once, priority circuits decide among them. Devices have unique priority levels, fixed at system installation. A unit with a high priority level obviously always takes precedence over one with a low priority level; in the case of units with equal priority levels, the one closest to the processor on the bus takes precedence over those further away.

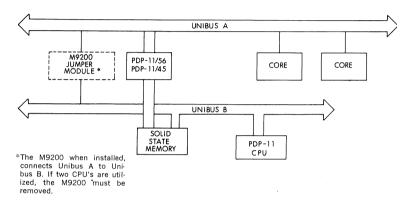

Figure 2-1 UNIBUS

Suppose the processor has control of the bus when three devices, all of higher priority than the processor, request bus control. If the requesting devices are of different priority, the processor will grant use of the bus to the one with the highest priority. If they are all of the same priority, all three signals come to the processor along the same bus line, so that it sees only one request signal. Its reply granting priority travels down the bus to the nearest requesting device, passing through any intervening non-requesting devices. The requesting device takes control of the bus, executes a single bus cycle of a few hundred nanoseconds, and relinquishes the bus. Then the request grant sequence occurs again, this time going to the second device down the line, which has been waiting its turn. When all higher-priority requests have been granted, control of the bus returns to the lowest-priority device, usually the processor.

The processor usually has lowest priority because in general it can stop whatever it is doing without serious consequences. Peripheral devices may be involved with some kind of mechanical motion, or may be connected to a real-time process, either of which requires immediate attention to a request, to avoid data loss.

The priority arbitration takes place asynchronously in parallel with data transfer. Every device on the bus except memory is capable of becoming a bus master.

## **BUS COMMUNICATION**

Communication is interlocked, so that each control signal issued by the master must be acknowledged by a response from the slave to complete the transfer. This simplifies the device interface because timing is no longer critical. The maximum typical transfer rate on the UNIBUS is one 16-bit word every 400 ns, or about 2.5 million 16-bit words per second.

## **USING THE BUS**

A device uses the bus if it needs to:

- Request the processor. As a result, the processor stops what it is doing, enters an interrupt service routine, and services the device.

- Transfer a word or byte of data to or from another device without involving the processor, an NPR (non-processor request) transfer. Such functions are performed by direct memory access devices such as disks or tape units.

Whenever two devices communicate, it is called a bus cycle. Only one word or byte can be transferred per bus cycle. An instruction cycle involves one or more bus cycles. Fetching an instruction involves a bus cycle; storing a result in memory or a device register involves another bus cycle.

## **BUS CONTROL**

There are two ways of requesting bus control: non-processor requests (NPRs) or bus requests (BRs).

A NPR is issued when a device wishes to perform a data transaction. A NPR does not use the CPU; therefore, the CPU can relinquish bus control while an instruction is being executed.

A BR is issued when a device needs to interrupt the CPU for service. An interrupt is not serviced until the processor has finished executing its current instruction.

## **BUS REQUESTS**

- DEVICE makes a bus request by asserting a BR.

- BUS ARBITRATOR recognizes the request by issuing a Bus Grant (BG). This bus grant is issued only if the priority of the device is greater than the priority currently assigned to the processor.

- DEVICE acknowledges the bus grant and inhibits further grants by asserting Selection Acknowledge (SACK). The device also clears BR.

- BUS ARBITRATOR receives SACK and clears BG.

- DEVICE asserts Bus Busy (BBSY) and clears SACK.

- DEVICE asserts Bus Interrupt (INTR) and its vector address.

## **NON-PROCESSOR REQUESTS**

- DEVICE makes a non-processor request by asserting NPR.

- BUS ARBITRATOR recognizes the request by issuing a non-processor grant or NPG.

- DEVICE acknowledges the grant and inhibits further grants by asserting SACK; device also clears NPR.

- BUS ARBITRATOR receives SACK and clears NPG.

- DEVICE asserts Bus Busy (BBSY) and clears SACK.

- DEVICE starts its data transaction.

## **BUS BUSY SIGNAL**

Once a device's bus request has been honored, it becomes bus master as soon as the current bus master relinquishes control.

- Current bus master relinquishes bus control by clearing bus busy (BBSY).

- New device assumes bus control by setting BBSY.

## INTERRUPTS

Interrupt handling is automatic in the PDP-11. No device polling is required to determine which service routine to execute. A device can interrupt the CPU only if it has gained bus control via a BR. The DEVICE requests an interrupt by asserting INTR along with an interrupt vector. The vector directs the CPU to a memory location which contains the starting address of an interrupt service routine. ("I need to interrupt.") The CPU accepts the interrupt vector and asserts SSYN (Slave YNc) to indicate the vector has been accepted. ("I have your interrupt.") The DEVICE releases the bus to the CPU by clearing INTR, removing the vector, and clearing BBSY. ("I'm giving control of the bus back to you.") The CPU acknowledges by clearing SSYN (Slave Sync), stores the information it needs to return to the interrupted program (a hardware stack located in memory is used for this purpose), and enters the interrupt handling sequence. ("Thank you, I'm starting to service your interrupt.") When the interrupt operation is completed, the CPU removes the information that was stored on the stack and resumes the program at the point where it was interrupted. A more detailed description of the operations required to service an interrupt follows:

- 1. Processor relinquishes control of the bus, priorities permitting.

- 2. When a master gains control, it sends the processor an interrupt request and a unique memory address which contains the address of the device's service routine, called the interrupt vector address. Immediately following this pointer address is a word (located at vector address +2) which is to be used as the new processor status word.

- The new PC and PS (interrupt vector) are taken from the specified address. The old PS and PC are then pushed onto the current stack. The service routine is then entered.

- 4. The device service routine can cause the processor to resume the interrupted process by executing the return from interrupt instruction, described in Chapter 4, which pops the two top words from the current processor stack and uses them to load the PC and PS registers.

A device routine can be interrupted by a higher priority bus request any time after the new PC and PS have been loaded. If such an interrupt occurs, the PC and PS of the service routine are automatically stored in the temporary registers and then pushed onto the new current stack, and the new device routine is entered.

## Interrupt Servicing

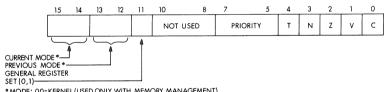

Every hardware device capable of interrupting the processor has a unique pair of locations (2 words) reserved for its interrupt vector. The first word contains the location of the device's service routine, and the second, the processor status word that is to be used by the service routine. Through proper use of the PS, the programmer can switch the operational mode of the processor, and modify the processor's priority level to mask out lower level interrupts.

## PRIORITY CONTROL

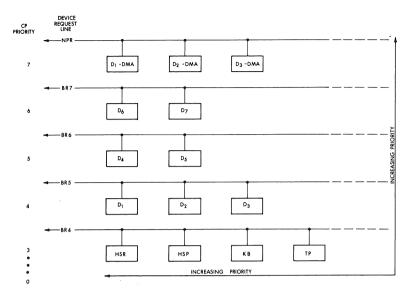

The PDP-11 priority system determines which device obtains the bus. Each PDP-11 device is assigned a specific location in the priority structure. Priority arbitration logic determines which device obtains the bus according to its position in the priority structure. The priority structure is 2-dimensional; i.e., there are vertical priority levels and horizontal priorities at each level. There are five vertical priority levels.

Devices that gain bus control with one of the bus request lines (BR7, BR6, BR5) can take full advantage of the power of the processor by requesting an interrupt. The entire instruction set is then available for manipulating data and status registers. When a device servicing program is being run, the task being performed by the processor is interrupted, and the device service routine is initiated. After the device request has been satisfied, the processor returns to its former task. Note that interrupt requests can be made only if bus control has been gained through a BR priority level.

## **Bus Request Level**

There are two lines associated with each BR level. The bus request is made on a BR line (BR7, BR6, BR5, or BR4). The bus grant is made on the corresponding grant line (BG7, BG6, BG5, or BG4). BR levels BR3 through BR0 are used only by the software; devices are not assigned to these BR levels. Unlike NPRs, a BR can be handled only between instruction cycles. The BR levels are used for interrupts so that the device can obtain service from the CPU. A request made at any BR level requires processor intervention.

## **Priority Levels**

Because there are only five vertical priority levels, NPR, BR7, BR6, BR5, and BR4, it is often necessary to connect more than one device to a single level. When a number of devices are connected to the same level, the situation is referred to a horizontal priority. If more than one device makes a request at the same level, then the device closest to the CPU has the highest priority.

Figure 2-2 Priority Control

The grant line for the NPR level is connected to all devices on that level in a "daisy chain" arrangement. When an NPG is issued, it first goes to the device closest to the CPU. If that device did not make the request, it permits the NPG to travel to the next device. Whenever the NPG reaches a device that has made a request, that device captures the grant, and prevents it from passing to any subsequent device in the chain.

BR chaining is identical to NPR chaining in function. However, each BR level has its own BG chain. Thus, the grant chain for BR7 is the BG7 line which is chained through all devices at the BR7 level.

## PRIORITY ASSIGNMENTS

When assigning priorities to a device, three factors must be considered: operating speed, ease of data recovery, and service requirements.

Data from a fast device is available for only a short time period. Therefore, highest priorities are usually assigned to fast devices to prevent loss of data and to prevent the bus from being tied up by slower devices.

If data from a device is lost, recovery may be automatic, may require manual intervention, or may be impossible. Therefore, highest priori-

ties are assigned to devices whose data cannot be recovered, while lowest priorities are reserved for devices with automatic data recovery features.

## **CPU Priority Level**

In addition to device priority levels, the CPU has a programmable priority. The CPU can be set to any one of eight priority levels. Priority is not fixed; it can be raised or lowered by software. The CPU priority is elevated from level 4 to level 6 when the CPU stops servicing a BR4 device and starts servicing a BR6 device. This programmable priority feature permits masking of bus requests. The CPU can hold off servicing lower priority devices until more critical functions are completed. For example, when CPU priority is set to level 6, all bus requests on the same and lower levels are ignored (in this case, all requests appearing on BR4, BR5, and BR6).

## **DATA TRANSACTIONS**

There are four types of data transactions:

- DATO a data word is transferred out of the master and into its slave.

- DATOB a data byte is transferred out of the master and into its slave.

- DATI a data word or byte is transferred into the master.

- DATIP used with destructive readout devices such as core memory. It is similar to a DATI except that data is not rewritten (restored) into the addressed memory location (data is restored during a DATI).

Must be followed by DATO or DATOB to the same location.

## **EXECUTION OF DATA TRANSACTIONS**

Before a device can perform a data transaction, it must:

- Obtain control of the bus via an NPR.

- Select (address) the slave device it wishes to communicate with.

Each device on the bus has a unique address.

- Tell the slave what type of data transaction is to be performed.

Data transactions between a master and slave device are synchronized by master sync (MSYN) and slave signals. Below is an example of how these signals are used during a typical DATI transaction:

Master selects the slave by addressing it, specifies the type of data transaction, and requests data by asserting MSYN.("Give me data.")

- 2. Slave gathers the data and asserts SSYN when the data is available. ("Here it is.")

- 3. Master drops MSYN after it accepts the data. ("Thank you, I have the data.")

- 4. Slave removes data from the lines and acknowledges the master by dropping SSYN. ("You're welcome.")

# Table 2-1 Bus Control

|            | -<br>-                            | <u> </u>               | ō                    | <u> </u>              | nt &<br>nts                                  | e<br>e                        | <u>5</u> :=                                                                          |

|------------|-----------------------------------|------------------------|----------------------|-----------------------|----------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------|

|            | Highest priority bus re-<br>quest | Transfers bus control  | Requests bus control | Transfers bus control | Acknowledges grant & inhibits further grants | Asserts control of the<br>bus | Transfers bus control<br>to handling routine in<br>the processor                     |

| TION       | st prio                           | fers bu                | sts bu               | fers bu               | wledg<br>s furth                             | ts cont                       | Transfers bus<br>to handling ro<br>the processor                                     |

| FUNCTION   | Highe:<br>quest                   | Transi                 | Reque                | Transl                | Ackno                                        | Asserl                        | Transi<br>to han<br>the pr                                                           |

|            | σ.                                | Ø                      | Ø                    | no                    |                                              | sno                           | by a<br>,<br>d af-                                                                   |

| <b>(</b> 5 | ıronou                            | ıronou                 | ıronou               | struct                | nse to<br>BG                                 | ed by b                       | ol has<br>ained l<br>t NPR)<br>sserte                                                |

| TIMING     | Asynchronous                      | Asynchronous           | Asynchronous         | After instruction     | Response to<br>NPG or BG                     | Asserted by bus<br>master     | If control has<br>been gained by a<br>BR (not NPR),<br>INTR asserted af-<br>ter BBSY |

| •          |                                   |                        |                      |                       |                                              |                               |                                                                                      |

| DEST.      | Memory                            | Next bus<br>master     | Memory               | Next bus<br>master    | Memory                                       | All devices                   | Memory                                                                               |

| DE         | ž                                 | N E                    |                      | ŽË                    | ž                                            | ¥                             | ž                                                                                    |

| RCE        | OMA<br>Se                         |                        | Any device           | ory                   | bus                                          | er                            | ē                                                                                    |

| SOURCE     | Any DMA<br>device                 | CPU                    | Any o                | Memory                | Next bus<br>master                           | Master                        | Master                                                                               |

|            | sor                               | sor                    |                      |                       |                                              |                               |                                                                                      |

|            | Non-processor<br>Request          | Non-processor<br>Grant | Bus Request          | rant                  | Selection Ac-<br>knowledge                   | nsy                           | tdr                                                                                  |

| NAME       | Non-pro<br>Request                | Non-p<br>Grant         | Bus R                | Bus Grant             | Selection A<br>knowledge                     | Bus Busy                      | Interrupt                                                                            |

| 1AL        |                                   |                        |                      |                       | ¥                                            | <b>&gt;</b> -                 |                                                                                      |

| SIGNAL     | N<br>R                            | NPG                    | BR7<br>thru<br>BR4   | BG7<br>thru<br>BG4    | SACK                                         | BBSY                          | R<br>R                                                                               |

|            |                                   |                        |                      |                       |                                              |                               |                                                                                      |

## **CHAPTER 3**

## **ADDRESSING MODES**

In the PDP-11, all memory reference addressing is accomplished using the eight general purpose registers. In specifying an address of the data (operand address), one of the eight registers is selected and one of several addressing modes. Each PDP-11 memory reference instruction specifies the:

- •function to be performed (operation code)

- general purpose register to be used when locating the source and/or destination operand

- addressing mode, which specifies how the selected registers are to be used

The instruction format and addressing techniques available to the programmer are of particular importance. It is in the combination of addressing modes with the instruction set that the PDP-11 provides a unique number of capabilities. The PDP-11 is designed to handle structured data both efficiently and with flexibility. The general purpose registers implement these functions in the following ways, by acting:

- •as accumulators: holding the data to be manipulated

- as pointers: The contents of the register are the address of the operand, rather than the operand itself, allowing automatic stepping through memory locations.

- as index registers: The contents of the register are added to the second word of the instruction to produce the address of the operand. This capabilty allows easy access to variable entries in a list.

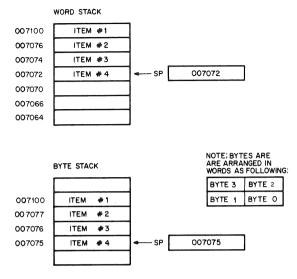

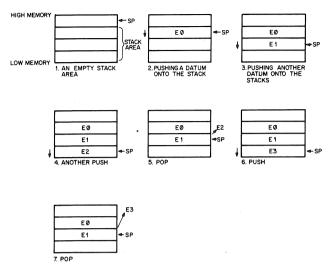

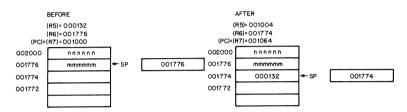

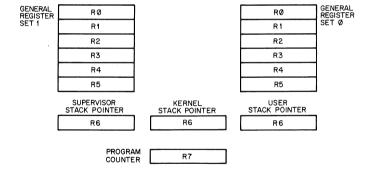

Utilization of the registers for both data manipulation and address calculation results in a variable length instruction format. If registers alone are used to specify the data source, only one memory word is required to hold the instruction. In certain modes, two or three words may be utilized to hold the basic instruction components. Special addressing mode combinations in the PDP-11 enable temporary data storage for convenient dynamic handling of frequently accessed data. This is known as **stack addressing**. Programming techniques utilizing the stack are discussed in Chapter 5. Register 6 is always used as the hardware stack pointer, or SP. Register 7 is used by the processor as its program counter (PC). Thus, the register arrangement to be considered in conjunction with instructions and with addressing modes is: registers 0-5 are general purpose registers, register 6 is the hardware

## ADDRESSING MODES

stack pointer, and register 7 is the program counter. The full PDP-11 instruction set and instruction formats are explained in Chapter 4.

For the purpose of clearly illustrating the use of the various addressing modes, the following instructions are used in this chapter:

| Mnemonic | Description                                                                                                                                   | Octal Code |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|

| CLR      | Clear (Zero the specified destination.)                                                                                                       | 0050DD     |

| CLRB     | Clear Byte (Zero the byte in the specified destination.)                                                                                      | 1050DD     |

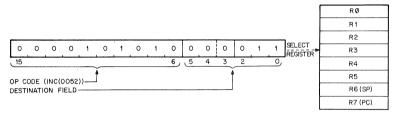

| INC      | Increment (Add 1 to contents of destination.)                                                                                                 | 0052DD     |

| INCB     | Increment Byte (Add 1 to the contents of destination byte.)                                                                                   | 1052DD     |

| СОМ      | Complement (Replace the contents of the destination by their logical 1's complements; each 0 bit is set and each 1 bit is cleared.)           | 0051DD     |

| СОМВ     | Complement Byte (Replace the contents of the destination byte by their logical 1's complements; each 0 bit is set and each 1 bit is cleared.) | 1051DD     |

ADD

Add (Add source operand to destination operand and store the result at destination address.)

DD = destination field (6 bits)

SS = source field (6 bits)

() = contents of

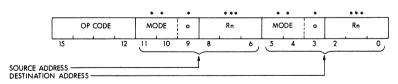

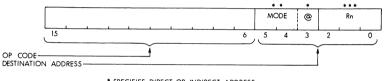

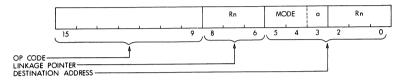

Single and double operand instructions utilize the following format.

The instruction format for the first word of all single operand instructions (such as clear, increment, test) is

Figure 3-1 Single Operand Instruction Format

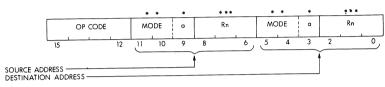

The instruction format for the first word of the double operand instruction is as follows:

- \* DIRECT DEFERRED BIT FOR SOURCE AND DESTINATION ADDRESS

- \*\* SPECIFIES HOW SELECTED REGISTERS ARE TO BE USED

- \*\*\* SPECIFIES A GENERAL REGISTER

Figure 3-2 Double Operand Instruction Format

## ADDRESSING MODES

Bits 3-5 specify the binary code of the addressing mode chosen.

The four direct addressing modes are:

- register

- autoincrement

- autodecrement

- index

When bit 3 of the instruction is set, indirect addressing is specified and the four basic modes become deferred modes. In a register deferred mode, the content of the selected register is taken as the address of the operand. In the other deferred modes, the content of the register specifies the address of the operand, rather than the operand itself. Prefacing the register operand(s) with an "@" sign or placing the register in parentheses indicates to the MACRO-11 assembler that deferred addressing mode is being used.

The indirect addressing modes are:

- register deferred

- autoincrement deferred

- autodecrement deferred

- •index deferred

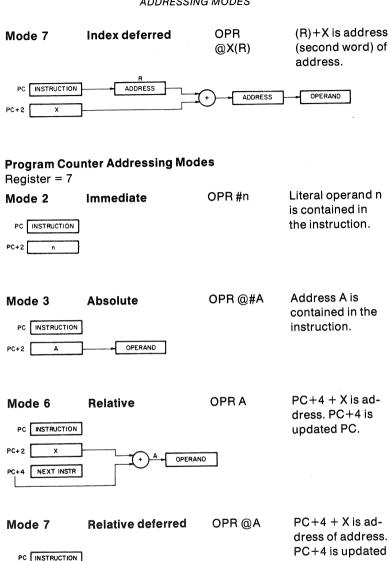

Program counter (register 7) addressing modes are:

- immediate

- absolute

- relative

- relative deferred

The PDP-11 addressing modes are explained and shown in examples in the following pages. They are summarized, in text and in graphic representation, at the end of the chapter.

## **REGISTER MODE**

MODE 0

Rn

Register mode provides faster instruction execution. There is no need to reference memory to retrieve an operand. Any of the general registers can be used as simple accumulators. The operand is contained in the selected register. Assembler syntax requires that a general register be defined as follows:

R0 = %0

R1 = %1

B2 = %2

% sign indicates register definition.

## **Register Mode Examples**

| Symbolic | Instruction<br>Octal Code | Description                  |

|----------|---------------------------|------------------------------|

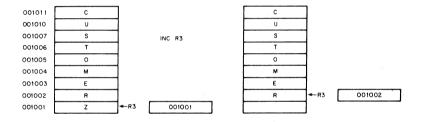

| INC R3   | 005203                    | Add 1 to the contents of R3. |

## Represented as:

Figure 3-3 Register Mode Example

| Symbolic  | Instruction<br>Octal Code | Description                                                                                       |

|-----------|---------------------------|---------------------------------------------------------------------------------------------------|

| ADD R2,R4 | 060204                    | Add the contents of R2 to the contents of R4, replacing the original contents of R4 with the sum. |

## Represented as:

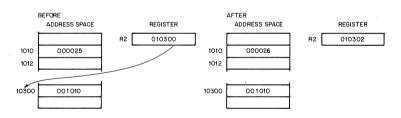

## REGISTER DEFERRED MODE MODE 1

In register deferred mode, the address of the operand is stored in a general purpose register. The address contained in the general purpose register directs the CPU to the operand. The operand is located outside the CPU, either in memory, or in an I/O register.

(Rn)

This mode is used for: sequential lists, indirect pointers in data structures, top of stack manipulations, and jump tables.

## ADDRESSING MODES

## **Register Deferred Mode Example**

| Symbolic | Instruction Octal<br>Code | Description                                               |

|----------|---------------------------|-----------------------------------------------------------|

| CLR (R5) | 005015                    | The contents of the location specified in R5 are cleared. |

## Represented as:

## **AUTOINCREMENT MODE**

MODE 2

(Rn)+

In autoincrement mode, the register contains the address of the operand; the address is automatically incremented after the operand is retrieved. The address then references the next sequential operand. This mode allows automatic stepping through a list or series of operands stored in consecutive locations. When an instruction calls for mode 2, the address stored in the register is autoincremented each time the instruction is executed. It is autoincremented by 1 if you are using byte instructions, by 2 if you are using word instructions.

## **Autoincrement Mode Example**

| Symbolic  | Instruction<br>Octal Code | Description                                                                                                               |

|-----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------|

| CLR (R5)+ | 005025                    | Contents of R5 are used as the address of the operand. Clear selected operand and then increment the contents of R5 by 2. |

## Represented as:

## **AUTOINCREMENT DEFERRED MODE**

MODE 3

@(Rn)+

In autoincrement deferred mode, the register contains a pointer to an address. The "+" indicates that the pointer in R2 is incremented by 2 after the address is located. Mode 2, autoincrement, is used only to access operands that are stored in consecutive locations. Mode 3, autoincrement deferred, is used to access lists of operands stored anywhere in the system; i.e., the operands do not have to reside in adjoining locations. Mode 2 is used to step through a table of volumes, mode 3 is used to step through a table of addresses.

## **Autoincrement Deferred Example**

| Symbolic   | Instruction<br>Octal Code | Description                                                                                                                               |

|------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| INC @(R2)+ | 005232                    | Contents of R2 are used as the address of the address of the operand. The operand is increased by 1, contents of R2 are incremented by 2. |

## Represented as:

## **AUTODECREMENT MODE**

MODE 4

-(Rn)

In autodecrement mode, the register contains an address that is automatically decremented; the decremented address is used to locate an operand. This mode is similar to autoincrement mode, but allows stepping through a list of words or bytes in reverse order. The address is autodecremented by 1 for bytes, by 2 for words.

## **Autodecrement Mode Example**

| Symbolic   | Instruction<br>Octal Code | Description                                                                                                           |

|------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------|

| INCB -(R0) | 105240                    | The contents of R0 are decremented by 1, then used as the address of the operand. The operand byte is increased by 1. |

## Represented as:

## **AUTODECREMENT DEFERRED MODE**

MODE 5

@-(Rn)

In autodecrement deferred mode, the register contains a pointer. The pointer is first decremented by 2, then the new pointer is used to retrieve an address stored outside the CPU. This mode is similar to autoincrement deferred, but allows stepping through a table of addresses in reverse order. Each address then redirects the CPU to an operand. Note that the operands do not have to reside in consecutive locations.

## **Autodecrement Deferred Mode Example**

| Symbolic   | Instruction<br>Octal Code | Description                                                                                                                          |

|------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| COM @-(R0) | 005150                    | The contents of R0 are decremented by 2 and then used as the address of the address of the operand. The operand is 1's complemented. |

## ADDRESSING MODES

## Represented as:

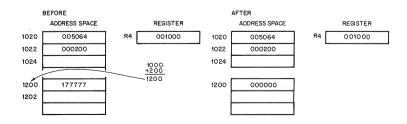

## **INDEX MODE**

MODE 6  $\pm X(Rn)$

In index mode, a base address is added to an index word to produce the effective address of an operand; the base address specifies the starting location of table or list. The index word then represents the address of an entry in the table or list relative to the starting (base) address. The base address may be stored in a register. In this case, the index word follows the current instruction. Or the locations of the base address and index word may be reversed (index word in the register, base address following the current instruction).

## **Index Mode Example**

| Symbolic    | Instruction<br>Octal Code | Description                                                                                                |

|-------------|---------------------------|------------------------------------------------------------------------------------------------------------|

| CLR 200(R4) | 005064<br>002000          | The address of the operand is determined by adding 200 to the contents of R4. The location is then cleared |

## Represented as:

#### INDEX DEFERRED MODE

MODE 7

@X(Rn)

In index deferred mode, a base address is added to an index word. The result is a pointer to an address, rather than the actual address. This mode is similar to mode 6, except that it produces a pointer to an address. The content of that address then redirects the CPU to the desired operand. Mode 7 provides for the random access of operands using a table of operand addresses.

### Index Deferred Mode Example

| Symbolic         | Instruction<br>Octal Code | Description                                                                                                                                                                            |

|------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add @1000(R2),R1 | 067201<br>001000          | 1000 and the contents of R2 are summed to produce the address of the address of the source operand, the contents of which are added to the contents of R1. The result is stored in R1. |

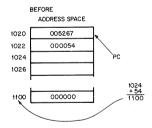

### Represented as:

#### **USE OF THE PC AS A GENERAL REGISTER**

Register 7 is both a general purpose register and the program counter on a PDP-11. When the CPU uses the PC to access a word from memory, the PC is automatically incremented by 2 to contain the address of the next word of the instruction being executed or the address of the next instruction to be executed. When the program uses the PC to access byte data, the PC is still incremented by 2.

The PC can be used with all the PDP-11 addressing modes. There are four modes in which the PC can provide advantages for handling position-independent code (see Chapter 5) and for handling unstructured data. These modes refer to the PC and are termed immediate, absolute (or immediate deferred), relative, and relative deferred.

### PC IMMEDIATE MODE

MODE 2

struction.

# n

Immediate mode is equivalent to using the autoincrement mode with the PC. It provides time improvements for accessing constant operands by including the constant in the memory location immediately following the instruction word.

# PC Immediate Mode Example

| PC Immediate Mode Example |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|---------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbolic                  | Instruction<br>Octal Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| ADD #10,R0                | 062700<br>000010          | The value 10 is located in the second word of the instruction and is added to the contents of R0. Just before this instruction is fetched and executed, the PC points to the first word of the instruction. The processor fetches the first word and increments the PC by two. The source operand mode is 27 (autoincrement the PC). Thus, the PC is used as a pointer to fetch the operand (the second word of the instruction) before being incremented by two to point to the next in- |  |  |

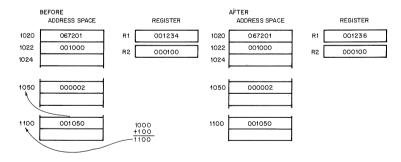

### Represented as:

#### PC ABSOLUTE MODE

MODE 3

@#A

This mode is the equivalent of immediate deferred or autoincrement deferred mode using the PC. The contents of the location following the instruction are taken as the address of the operand. Immediate data is interpreted as an absolute address (i.e., an address that remains constant no matter where in memory the assembled instruction is executed).

# **PC Absolute Mode Example**

| Symbolic   | Instruction<br>Octal Code | Description                           |

|------------|---------------------------|---------------------------------------|

| CLR @#1100 | 005037<br>001100          | Clears the contents of location 1100. |

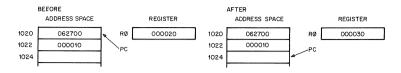

### Represented as:

#### PC RELATIVE MODE

MODE 6

A

This mode is index mode 6 using the PC. The operand's address is calculated by adding the word that follows the instruction (called an "offset") to the updated contents of the PC.

PC+2 directs the CPU to the offset that follows the instruction. PC+4 is summed with this offset to produce the effective address of the operand. PC+4 also represents the address of the next instruction in the program.

With the relative addressing mode, the address of the operand is always determined with respect to the updated PC. Therefore, when the instruction is relocated, the operand remains the same relative distance away.

The distance between the updated PC and the operand is called an **offset**. After a program is assembled, this offset appears in the first word location that follows the instruction. This mode is useful for writing position-independent code (see Chapter 5).

### **PC Relative Mode Example**

| Symbolic | Instruction<br>Octal Code | Description                                                                                                                                                        |

|----------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INC A    | 005267<br>000054          | To increment location A, contents of memory location in the second word of the instruction are added to PC to produce address A. Contents of A are increased by 1. |

### Represented as:

### PC RELATIVE DEFERRED MODE

MODE 7

@A

This mode is index deferred (mode 7), using the PC. A pointer to an operand's address is calculated by adding an offset (that follows the instruction) to the updated PC.

This mode is similar to the relative mode, except that it involves one additional level of addressing to obtain the operand. The sum of the offset and updated PC (PC+4) serves as a pointer to an address. When the address is retrieved, it can be used to locate the operand.

# PC Relative Deferred Mode Example

| Symbolic | Instruction<br>Octal Code | Description                                                                                                         |

|----------|---------------------------|---------------------------------------------------------------------------------------------------------------------|

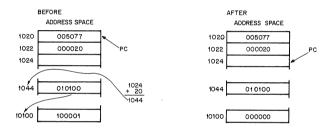

| CLR @A   | 005077<br>000020          | Adds the second word of the instruction to PC to produce the address of the address of the operand. Clears operand. |

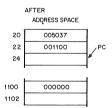

# Represented as:

**Table 3-1 Direct Addressing Modes**

| Binary<br>Code | Mode | Name          | Symbolic | Function                                                                          |

|----------------|------|---------------|----------|-----------------------------------------------------------------------------------|

| 000            | 0    | Register      | Rn       | Register contains operand.                                                        |

| 010            | 2    | Autoincrement | (Rn)+    | Register is used<br>as a pointer to<br>sequential data,<br>then increment-<br>ed. |

| Binary<br>Code | Mode | Name          | Symbolic           | Function                                                                                                 |

|----------------|------|---------------|--------------------|----------------------------------------------------------------------------------------------------------|

| 100            | 4    | Autodecrement | —(Rn) <sub>,</sub> | Register is de-<br>cremented and<br>then used as a<br>pointer to se-<br>quential data.                   |

| 110            | 6    | Index         | X(Rn)              | Value X is added<br>to (Rn) to pro-<br>duce address of<br>operand. Neither<br>X nor (Rn) is<br>modified. |

Table 3-2 summarizes the same four basic modes used with indirect addressing.

**Table 3-2 Indirect Addressing Modes**

| Binary<br>Code | Mode | Name                      | Symbolic       | Function                                                                                                                                         |

|----------------|------|---------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 001            | 1    | Register De-<br>ferred    | @Rn or<br>(Rn) | Register contains<br>the address of<br>the operand.                                                                                              |

| 011            | 3    | Autoincrement<br>Deferred | @(Rn)+         | Register is first used as a pointer to a word containing the address of the operand, then incremented (always by 2, even for byte instructions). |

| Binary<br>Code | Mode | Name                      | Symbolic | Function                                                                                                                                                                                      |

|----------------|------|---------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 101            | 5    | Autodecrement<br>Deferred | @-(Rn)   | Register is decremented (always by 2, even for byte instructions) and then used as a pointer to a word containing the address of the operand.                                                 |

| 111            | 7    | Index Deferred            | @X(rn)   | Value X (located in a word contained in the instruction) and (Rn) are added and the sum is used as a pointer to a word containing the address of the operand. Neither X nor (Rn) is modified. |

When used with the PC, these modes are termed immediate, absolute (or immediate deferred), relative, and relative deferred, and are summarized in Table 3-3.

Table 3-3 PC Register Addressing Modes

| Binary<br>Code | Mode | Name      | Symbolic | Function                                 |

|----------------|------|-----------|----------|------------------------------------------|

| 010            | 2    | Immediate | #n       | Operand is contained in the instruction. |

| Binary<br>Code | Mode | Name              | Symbolic | Function                                                                                                   |

|----------------|------|-------------------|----------|------------------------------------------------------------------------------------------------------------|

| 011            | 3    | Absolute          | @#A      | Absolute address is contained in the instruction.                                                          |

| 110            | 6    | Relative          | A        | Address of A, re-<br>lative to the in-<br>struction, is con-<br>tained in the<br>instruction.              |

| 111            | 7    | Relative Deferred | @A       | Address of location containing address of A, relative to the instruction, is contained in the instruction. |

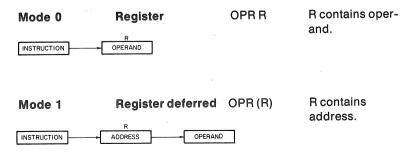

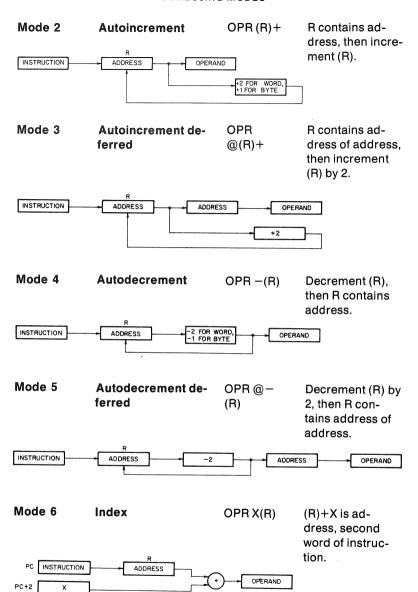

# **GRAPHIC SUMMARY OF PDP-11 ADDRESSING MODES**

# **General Register Addressing Modes**

R is a general register, 0 to 7.

(R) is the contents of that register.

ADDRESS

PC+2

PC+4 NEXT INSTR

PC.

OPERAND

### **CHAPTER 4**

# **INSTRUCTION SET**

The PDP-11 instruction set and addressing modes produce over 400 unique instructions. The instruction set offers a wide choice of operations, so that a single instruction will frequently accomplish a task that would require several in a traditional computer. PDP-11 instructions allow byte and word addressing in both single and double operand formats. This saves memory space and simplifies the implementation of control and communications applications. The PDP-11's use of double operand instructions allows you to perform several operations with a single instruction. For example, ADD A,B adds the contents of location A to location B, storing the result in location B. Traditional computers would implement this instruction in the following way:

CLR A,C LDA A ADD B STR B

The PDP-11 instruction set also contains a full set of conditional branches, eliminating excessive use of jump instructions. All PDP-11 instructions fall into one of three categories:

- Single Operand one part of the word specifies the operation, referred to as "op code," the second part provides information for locating the operand.

- Double Operand the first part of the word specifies the operation to be performed, the remaining two parts provide information for locating two operands.

- Program Control the first part of the word specifies the operation to be performed, the second part indicates where the action is to take place in the program.

### SINGLE OPERAND INSTRUCTIONS

|         | Mnemonic | Instruction               |

|---------|----------|---------------------------|

| General |          |                           |

|         | CLR(B)   | clear destination         |

|         | COM(B)   | 1's complement dst        |

|         | INC(B)   | increment dst             |

|         | DEC(B)   | decrement dst             |

|         | NEG(B)   | 2's complement negate dst |

|         | TST(B)   | test dst                  |

|         |          |                           |

|               | Mnemonic                                     | Instruction                                                                                        |

|---------------|----------------------------------------------|----------------------------------------------------------------------------------------------------|

| Shift & Rotat | е                                            |                                                                                                    |

|               | ASR(B)<br>ASL(B)<br>ROR(B)<br>ROL(B)<br>SWAB | arithmetic shift right<br>arithmetic shift left<br>rotate right<br>rotate left<br>swap bytes       |

| Multiple Pred | cision                                       |                                                                                                    |

|               | ADC(B)<br>SBC(B)<br>SXT<br>MFPS<br>MTPS      | add carry subtract carry sign extend move byte from processor status Move byte to processor status |

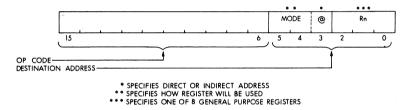

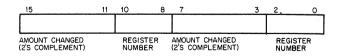

### Instruction Format

- \* SPECIFIES DIRECT OR INDIRECT ADDRESS

\*\* SPECIFIES HOW REGISTER WILL BE USED

\*\*\* SPECIFIES ONE OF 8 GENERAL PURPOSE REGISTERS

Figure 4-1 Single Operand Instruction Format

The instruction format for single operand instructions is:

- Bit 15 indicates word or byte operation.

- Bits 14-6 indicate the operation code, which specifies the operation to be performed.

- Bits 5-0 indicate the 3-bit addressing mode field and the 3-bit general register field. These two fields are referred to as the destination field.

# **DOUBLE OPERAND INSTRUCTIONS**

| Mnemonic | Instruction                                    |

|----------|------------------------------------------------|

|          |                                                |

| MOV(B)   | move source to destination add src to dst      |

| SUB      | subtract src from dst                          |

| ASHC     | shift arithmetically arithmetic shift combined |

|          | MOV(B)<br>ADD<br>SUB<br>ASH                    |

|         | Mnemonic | Instruction  |

|---------|----------|--------------|

| Logical |          |              |

|         | BIT(B)   | bit test     |

|         | BIC(B)   | bit clear    |

|         | BIS(B)   | bit set      |

|         | XOR      | exclusive OR |

### **Instruction Format**

- \* DIRECT DEFERRED BIT FOR SOURCE AND DESTINATION ADDRESS

- \*\* SPECIFIES HOW SELECTED REGISTERS ARE TO BE USED

- \*\*\* SPECIFIES A GENERAL REGISTER

Figure 4-2 Double Operand Instruction Format

The format of most double operand instructions is similar to that of single operand instructions except that they have *two* fields for locating operands. One field is called the source field, the other is called the destination field. Each field is further divided into addressing mode and selected register. Each field is completely independent. The mode and register used by one field may be completely different than the mode and register used by another field.

- Bit 15 indicates word or byte operation except when used with op code 6. Then it indicates an ADD or SUBtract instruction.

- Bits 14-12 indicate the op code, which specifies the operation to be done.

- Bits 11-6 indicate the 3-bit addressing mode field and the 3-bit general register field. These two fields are referred to as the source field.

- Bits 5-0 indicate the 3-bit addressing mode field and the 3-bit general register field. These two fields are referred to as the **destination** field.

# **Byte Instructions**

Byte instructions are specified by setting bit 15. Thus, in the case of the MOV instruction, bit 15 is 0; when bit 15 is set, the mnemonic is MOVB. There are no byte operations for ADD and SUB, i.e., no ADDB or SUBB.

# PROGRAM CONTROL INSTRUCTIONS

| Branch Instr       | uctions        |                                         |

|--------------------|----------------|-----------------------------------------|

|                    | Mnemonic       | Instruction                             |

| Branch             |                |                                         |

|                    | BR             | branch (unconditional)                  |

|                    | BNE            | branch if not equal (to zero)           |

|                    | BEQ            | branch if equal (to zero)               |

|                    | BPL            | branch if plus                          |

|                    | ВМІ            | branch if minus                         |

|                    | BVC            | branch if overflow is clear             |

|                    | BVS            | branch if overflow is set               |

|                    | BCC            | branch if carry is clear                |

|                    | BCS            | branch if carry is set                  |

| Signed Cond        | litional Branc | h                                       |

|                    | BGE            | branch if greater than or               |

|                    |                | equal (to zero)                         |

|                    | BLT            | branch if less than (zero)              |

|                    | BGT            | branch if greater than (zero)           |

| 1                  | BLE            | branch if less than or                  |

|                    |                | equal (to zero)                         |

|                    | SOB            | subtract one and branch (if not $= 0$ ) |

| <b>Unsigned Co</b> | nditional Bra  | nch                                     |

|                    | ВНІ            | branch if higher                        |

|                    | BLOS           | branch if lower or same                 |

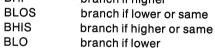

### Instruction Format

Figure 4-3 Branch Instruction Format

- The high byte (bits 8-15) of the instruction is an op code specifying the conditions to be listed.

- The low byte (bits 0-7) of the instruction is the offset value in words that determines the new program location if the branch is taken.

# JUMP AND SUBROUTINE INSTRUCTIONS

|   |   |   | Millellionic |  |

|---|---|---|--------------|--|

| _ | _ | _ |              |  |

Instruction

### Jump & Subroutine

JMP

jump

JSR RTS jump to subroutine return from subroutine

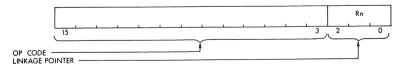

Instruction Format JSR Format

Figure 4-4 JSR Instruction Format

- Bits 9-15 are always octal 004 indicating the op code for JSR.

- Bits 6-8 specify the link register. Any general purpose register may be used in the link, except R6.

- •Bits 0-5 designate the destination field that consists of addressing mode and general register fields. This specifies the starting address of the subroutine.

- Register R7 (The Program Counter) is frequently used for both the link and the destination. For example, you may use JSR R7, SUBR, which is coded 004767. R7 is the only register that can be used for both the link and destination, the other GPRs cannot. Thus, if the link is R5, any register except R5 can be used for one destination field.

#### **RTS Format**

Figure 4-5 RTS Instruction Format

The RTS (return from subroutine) instruction uses the link to return control to the main program once the subroutine is finished.

- Bits 3-15 always contain octal 00020, which is the op code for RTS.

- Bits 0-2 specify any one of the general purpose registers.

The register specified by bits 0-2 must be the same register used as the link between the JSR causing the jump and the RTS returning control.

Instruction

### Interrupts and Traps

| EMT  | emulator trap         |

|------|-----------------------|

| TRAP | trap '                |

| BPT  | breakpoint trap       |

| IOT  | input/output trap     |

| RTI  | return from interrupt |

| RTT  | return from interrupt |

There are three ways of leaving a main program:

Mnemonic

- software exit the program specifies a jump to some subroutine

- trap exit internal hardware on a special instruction forces a jump to an error handling routine

- interrupt exit external hardware forces a jump to an interrupt service routine

In all of the above cases, there is a jump to another program. Once that program has been executed, control is returned to the proper point in the main program.

Instruction

### **MISCELLANEOUS INSTRUCTIONS**

Mnemonic

| MILLELLIQUIC | mstruction                           |

|--------------|--------------------------------------|

| HALT         | halt                                 |

| WAIT         | wait for interrupt                   |

| RESET        | reset UNIBUS                         |

| MTPD         | move to previous data space          |

| MTPI         | move to previous instruction space   |

| MFPD         | move from previous data space        |

| MFPI         | move from previous instruction space |

| MTPS         | move byte to processor status word   |

| MFPS         | move byte from                       |

|              | processor status word                |

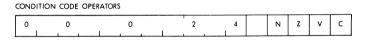

#### **CONDITION CODE OPERATION**

| Mnemonic            | Instruction |

|---------------------|-------------|

| CLC,CLV,CLZ,CLN,CCC | clear       |

| SEC,SEV,SEZ,SEN,SCC | set         |

There are four condition code bits:

- N, indicating a negative condition when set to 1

- Z, indicating a zero codition when set to 1

- V, indicating an overflow condition when set to 1

- •C, indicating a carry condition when set to 1

These four bits are part of the processor status word (PS). The result of any single operand or double operand instruction affects one or more of the four condition code bits. A new set of condition codes is usually created after execution of each instruction. Some condition codes are not affected by the execution of certain instructions. The CPU may be asked to check the condition codes after execution of an instruction. The condition codes are used by the various instructions to check software conditions.

**Z** bit — Whenever the CPU sees that the result of an instruction is zero, it sets the Z bit. If the result is not zero, it clears the Z bit. There are a number of ways of obtaining a zero result:

- adding two numbers equal in magnitude but different in sign

- comparing two numbers of equal value

- using the CLR instruction

N bit — The CPU looks only at the sign bit of the result. If the sign bit is set, indicating a negative value, the CPU sets the N bit. If the sign bit is clear, indicating a positive value, then the CPU clears the N bit.

C bit — The CPU sets the C bit automatically when the result of an instruction has caused a carry out of the most significant bit of the result. When the instruction results in a carry out of the most significant bit of the result, the carry itself is usually moved into the C bit. Otherwise, the C bit is cleared. During rotate instructions (ROL and ROR), the C bit forms a buffer between the most significant bit and the least significant bit of the word. A carry of 1 sets the C bit while a carry of 0 clears the C bit. However, there are exceptions. For example:

- SUB and CMP set the C bit when there is no carry.

- INC and DEC do not affect the C bit.

- COM always sets the C bit, TST always clears the C bit.

${f V}$  bit — The  ${f V}$  bit is set to indicate that an overflow condition exists. An overflow means that the result of an instruction is too large to be placed in the destination. There are two methods the hardware uses to check for an overflow condition.

One way is for the CPU to test for a change of sign.

- When using single operand instructions, such as INC, DEC, or NEG, a change of sign indicates an overflow condition.

- When using double operand instructions, such as ADD, SUB, or CMP, in which both the source and destination have like signs, a change of sign in the result indicates an overflow condition.

Another method used by the CPU is to test the N bit and C bit when dealing with shift and rotate instructions.

- If only the N bit is set, an overflow exists.

- If only the C bit is set, an overflow exists.

- If both the N and C bits are set, there is no overflow condition.

More than one condition code can be set by a particular instruction. For example, both a carry and an overflow condition may exist after instruction execution.

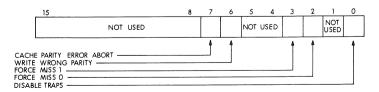

Figure 4-6 Condition Code Operators' Format

#### Instruction Format

The format of the condition code operators is as follows:

- •Bits 15-5 the "op" code

- Bit 4 the "operator" which indicates set or clear with the values 1 and 0 respectively. If set, any selected bit is set; if clear, any selected bit is cleared.

- Bits 3-0 the "select" field. Each of these bits corresponds to one of the four condition code bits. When one of these bits is set, then the corresponding condition code bit is set or cleared depending on the state of the "operator" (bit 4).

### **EXAMPLES**

The following examples and explanations illustrate the use of the various types of instructions in a program.

# Single Operand Instruction Example

This routine uses a tally to control a loop, which clears out a specific block of memory. The routine has been set up to clear 30<sub>8</sub>byte locations beginning at memory address 600.

(R0) = 600

(R1) = 30

LOOP: CLRB(R0)+

DEC R1 BNE R1 LOOP HALT

### **Program Description**

- The CLRB (R0)+ instruction clears the content of the location specified by R0 and increments R1.

- R0 is the pointer.

- Because the auto-increment addressing mode is used, the pointer automatically moves to the next memory location after execution of the CLRB instruction.

- Register R1 indicates the number of locations to be cleared and is, therefore, a counter. Counting is performed by the DEC R1 instruction. Each time a location is cleared, it is counted by decrementing R1.

- •The Branch If Not Zero, BNE, instruction checks for done. If the counter is not zero, the program branches back to start to clear another location. If the counter is zero, indicating done, then the program executes the next instruction, HALT.

### **Double Operand Instruction Example**

This routine prints out a portion of a payroll program for review by the supervisor. It is known that 76 locations are to be printed and the locations start at address 600.

INIT:

MOV #600, R0

MOV #76, R1

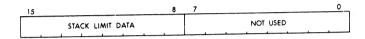

START: