# Small Systems Training PDP-11V23-/11T23 System Maintenance

Student Guide

### PDP-11V23/11T23 SYSTEM MAINTENANCE EY-DX056-SP-002 J6269-A

STUDENT GUIDE

EY-DX052-SG-002

# Copyright 0 1980, 1981 by Digital Equipment Corporation All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| DIGITAL | DECsystem-10 | MASSBUS |

|---------|--------------|---------|

| DEC     | DECSYSTEM-20 | OMNIBUS |

| PDP     | DIBOL        | os/8    |

| DECUS   | EduSystem    | RSTS    |

| UNIBUS  | VAX          | RSX     |

|         | VMS          |         |

#### CONTENTS

Course Guide

11V23/11T23 Introduction

LSI-11/23 Bus Concepts

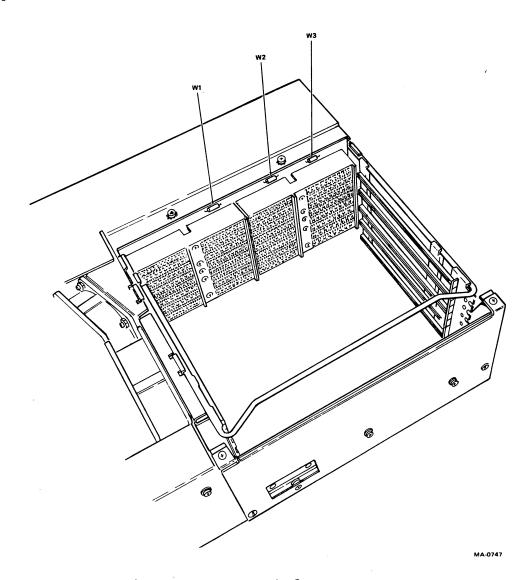

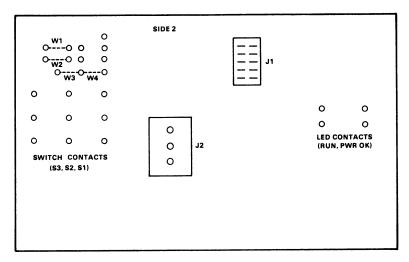

BAll-N Mounting Box

KDF11-AA Processor

MSV11-DD Memory

DLV11-J SLU

BDV11-AA Boot/Terminator

11V23/11T23 System Laboratory

PDP-11V23/11T23 SYSTEM MAINTENANCE

COURSE GUIDE

#### Course Guide

#### COURSE DESCRIPTION

The PDP-11V23/11T23 System Maintenance Course is a self-paced, lab-oriented course. It is designed to teach field service engineers the skills required to maintain the 11V23 and 11T23 systems in accordance with the prescribed maintenance philosophy. These skills include:

- o Installation

- o Loading and running diagnostics

- o Interpreting diagnostic messages

- o Configuring jumpers and switches

- o Theory of operation

- o Fault isolation

#### PREREQUISITES

The prerequisites for the PDP-11V23/11T23 System Maintenance Course are:

- o RLØl Disk Drive SPI course

- o RX02 Floppy Disk SPI course

- o VT100 Video Terminal SPI course

- o Introduction to PDP-11 Audio/Visual course

#### COURSE GOALS

After you complete this course you will be able to:

- Understand the physical relationships between all system elements.

- Identify the names and physical locations of switches, indicators, controls, and Field Replaceable Units (FRU).

- Operate the applicable device or system.

- Configure the switches and jumpers for particular applications or configurations.

- Using available maintenance and diagnostic aids, troubleshoot system malfunctions.

- Install an llV23/llT23 system.

#### MAINTENANCE PHILOSOPHY

The PDP-11V23/11T23 will be maintained on-site by the field service engineer. Maintenance consists of removal and replacement of FRUs to the module or subassembly level. The microprocessor chip set is considered an FRU.

FRUs, when found to be defective, are replaced using maintenance and diagnostic aids. These aids consist of three groups of diagnostics and a PDP-11V23 Troubleshooting Guide.

The most basic diagnostic tool is the hardware on-line debugging technique (ODT). This is built into the computer processor and consists of a group of commands and routines for locating error conditions and for communicating with the computer in simple commands and responses. Use of ODT will be covered in the KDF11-AA Processor course module.

The next group of diagnostic programs is built into the computer hardware and is located on the BDV11 circuit card (M8Ø12-YA module) in the form of three small programs. One of these programs automatically checks non-memory-modifying processor instructions during the power-on sequence. The remaining two programs check memory-modifying processor instructions and system memory. Use of these diagnostics will be covered in the BDV11 Boot/Terminator course module.

The RYDP or RLDP diagnostic software system consists of a collection of diagnostic programs plus monitor and utility programs stored on floppy disks or disk pack. The RYDP and RLDP programs are designed to diagnose individual system components. The use of these individual diagnostics will be discussed in the various course modules training.

The PDP-11V23 Troubleshooting Guide is designed to detect problems that prevent the loading and execution of diagnostics. Use of this manual will be covered in the 11V23/11T23 System Laboratory course module.

#### COURSE OUTLINE

- 1 11V23/11T23 Introduction

- A. PDP-11V23 System Overview

- B. PDP-11T23 System Overview

- C. PDP-11V23/11T23 Options

- 2 LSI-11/23 Bus Concepts

- A. Bus Identification

- B. Bus Basics

- C. Bus Cycles

- D. Data Transfers and Priority

- E. Special Bus Functions

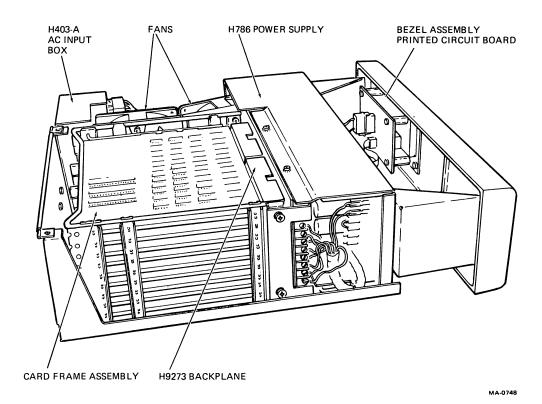

- 3 BAll-N Mounting Box

- A. Overview

- B. Physical/Functional Description

- C. Configuring

- D. Disassembly

- E. Adjustments

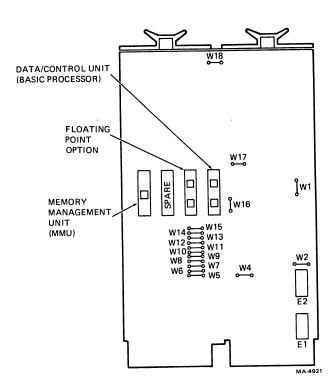

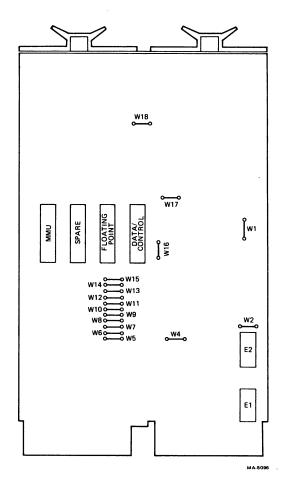

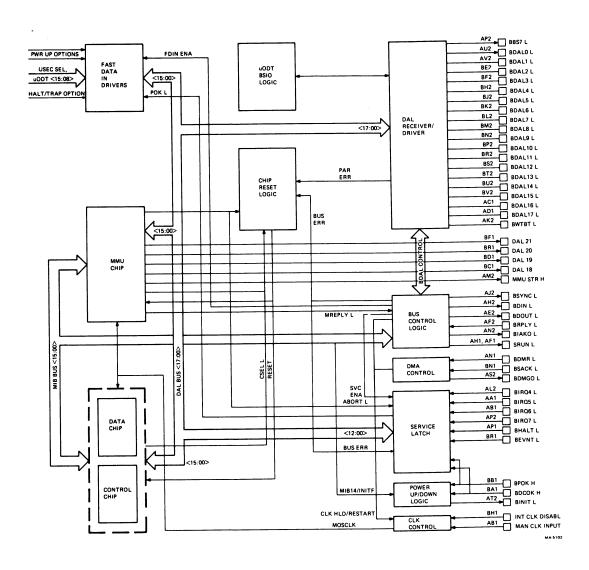

- 4 KDF11-AA Processor

- A. Overview

- B. Physical/Functional Description

- C. Theory of Operation

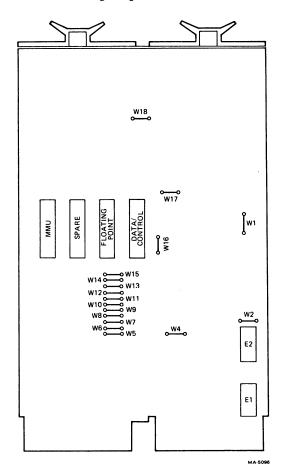

- D. Configuring

- E. Installation

- F. Operation

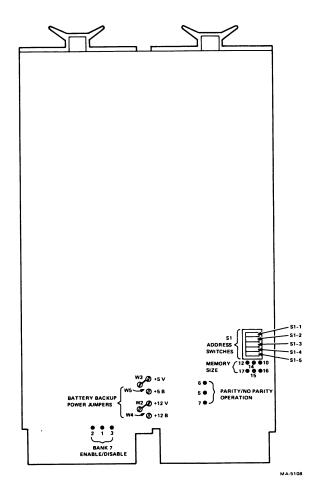

- 5 MSV11-DD 32K Dynamic MOS Memory

- A. Overview

- B. Physical/Functional Description

- C. Theory of Operation

- D. Configuring

- E. Installation

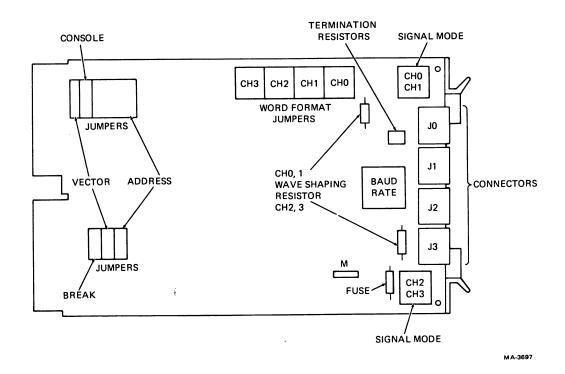

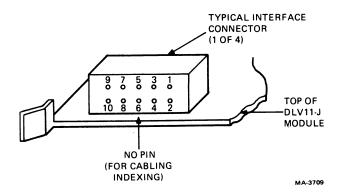

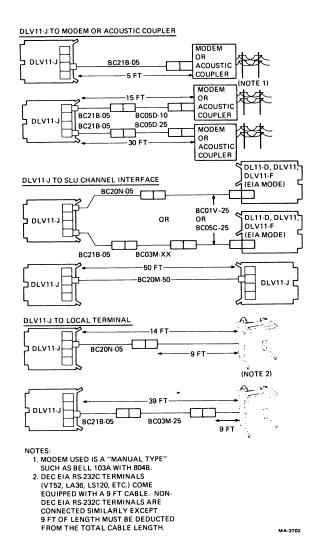

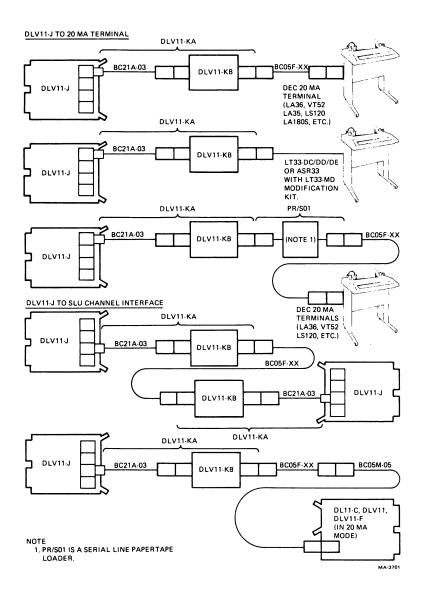

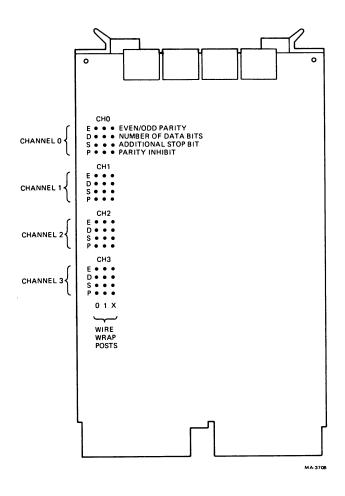

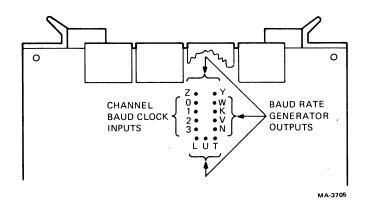

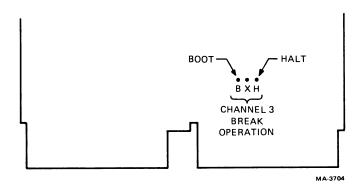

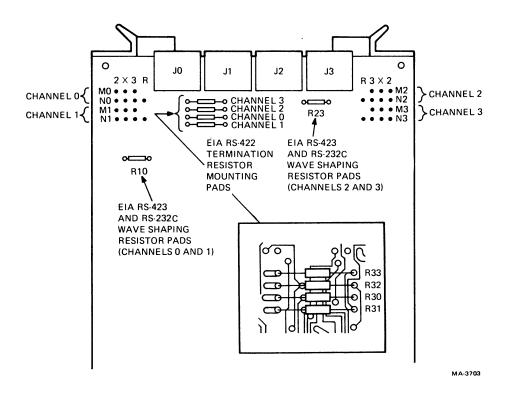

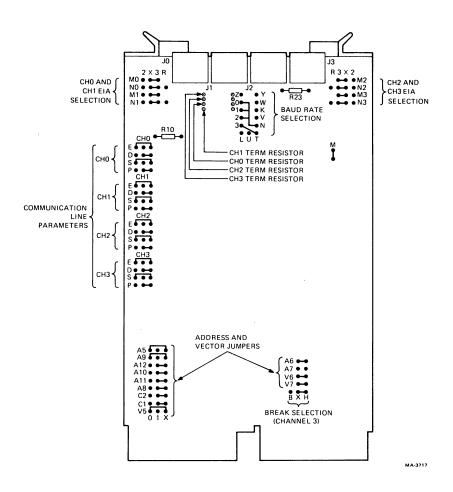

- 6 DLV11-J Serial Line Unit

- A. Overview

- B. Physical/Functional Description

- C. Configuring

- D. Installation

- E. Programming

- F. Troubleshooting

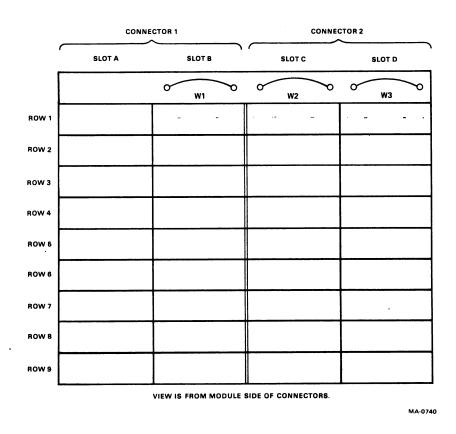

#### BDV11-AA Boot/Terminator 7

- Α. Overview

- Physical/Functional Description В.

- Programming C.

- D. ConfiguringE. Theory of Operation

- E. Diagnostic

#### 11V23/11T23 System Laboratory 8

- Installation Α.

- B. Acceptance

- C. Fault Isolation

#### COURSE ORIENTATION

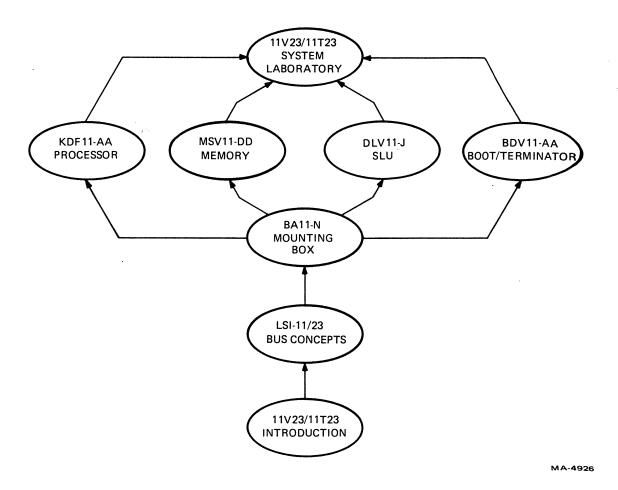

The course material is presented in a series of modules (Figure 1). Related modules are grouped together. You will work through each module by reading and doing exercises with an 11V23 or 11T23 system in the lab. You are encouraged to work at your own speed, either alone or with another student. A Course Administrator will be present at all times to help you with any difficulties or questions.

Figure 1. Course Map

Each module has at least one objective that states what you must be able to do to complete that module. To clarify these objectives, sample test items follow them. These show you the exact form in which you will be tested on the module's objectives.

There are at least four resources for each module: (1) the module itself, (2) other students, (3) the Course Administrator, and (4) additional resources. The additional resources may be the main source of information for the module or they may simply be additional suggested readings.

When borrowing an additional resource:

- Fill in the signout card or write your name on the Resource Signout Sheet.

- Cross out your name when you return the resource.

- Borrow only one resource at a time.

- Return all resources upon completion of the course.

Remember that you may request the help of the Course Administrator or another student (provided neither of you is working on a test) at any time.

The module text begins after the list of additional resources. The text presents information, directs you to additional resources, and instructs you to do related exercises. Work through this material at a comfortable speed, talking to your Course Administrator and the other students as necessary.

When you think that you can meet the module objectives, ask for the Module Test. This test covers only the material stated in the objectives and is similar in form to the sample test items.

For written tests:

- Use any reference material.

- There is no time limit.

- There is only one correct response.

- Work alone.

When you complete the test, submit it to the Course Administrator for evaluation (an 80% performance level is considered successful completion). If you have fulfilled the objective, the Course Administrator will sign your Personal Progress Plotter and the Master Progress Plotter. At this point, you may go on to another module. There are no penalties for not answering 80% of the questions correctly. You will simply be asked to review the test and exercise.

For performance/lab exercises:

- There is no time limit.

- Complete all steps.

- Observe safety precautions.

- Work alone.

If you think that you can meet the module objectives without reading its text or doing its performance/lab exercises, you may ask for the Module Test.

### PERSONAL PROGRESS PLOTTER

| Module Title                | Date<br>Achieved | Administrator<br>Signoff |

|-----------------------------|------------------|--------------------------|

| 11V23/11T23 Introduction    |                  |                          |

| LS1-11/23 Bus Concepts      |                  |                          |

| BAll-N Mounting Box         |                  |                          |

| KDF11-AA Processor          |                  |                          |

| MSV11-DD Memory             |                  |                          |

| DLV11-J SLU                 |                  |                          |

| BDV11-AA Boot/Terminator    |                  |                          |

| 11V23/11T23 System Laborato | ry               |                          |

### PDP-11V23/11T23 SYSTEM MAINTENANCE 11V23/11T23 INTRODUCTION

#### 11V23/11T23 Introduction

#### INTRODUCTION

This module will give you an overview of the PDP-11V23 and PDP-11T23 system. You will learn about the systems' appearances, specifications, and component parts. Details of how these systems operate will be covered in later modules.

#### OBJECTIVE ----

Identify the major component locations, specifications, and system capabilities of the PDP-11V23 and PDP-11T23 systems.

#### SAMPLE TEST ITEM

The PDP-11V23, when used with a VT100 video terminal, draws \_\_\_\_\_ watts from the ac power line.

- a. 860

- b. 1300

- c. 960

- d. 905

#### PDP-11V23 SYSTEM OVERVIEW

The PDP-11V23 is a general-purpose microcomputer system used for developing and executing programs for a variety of applications. Optional hardware and software are available for such applications as high-level language program development, foreground/background real-time support, multiprogramming, and the capability to monitor and control equipment. The basic PDP-11V23 does not include a terminal. DIGITAL can provide either a LA120 DECwriter III, a LA34/LA38 DECwriter IV, or a VT100 terminal as optional equipment.

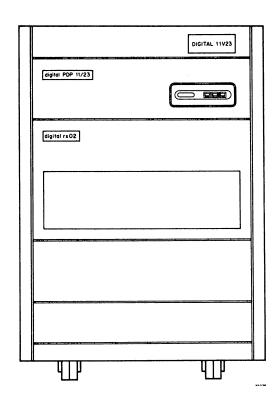

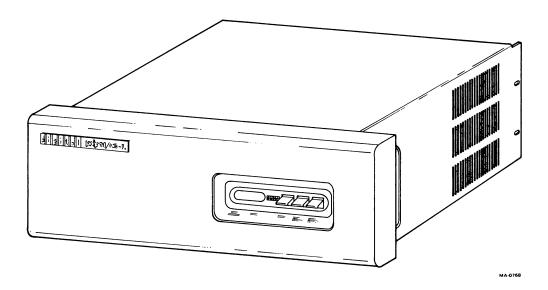

The PDP-11V23 (Figure 1) includes an operator's switch panel, a microcomputer with memory management functions, 64K word (128K byte) MOS memory (expandable to 128K word or 256K byte), a four channel serial line interface, and a dual floppy disk drive. Each disk drive provides 512K bytes of storage using double density format. Communication between user and microcomputer takes place via an optional system terminal (either a DECwriter or DECscope). A special bootstrap ROM terminator module initiates the system software when the system is turned on and can automatically test the system.

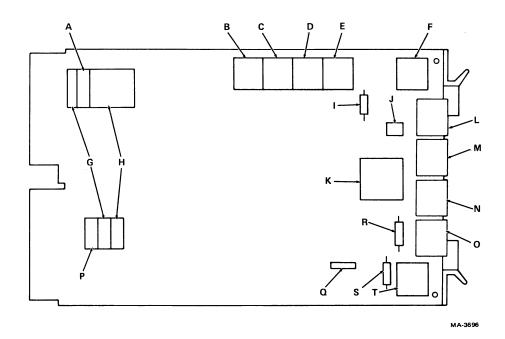

Figure 1. PDP-11V23 System

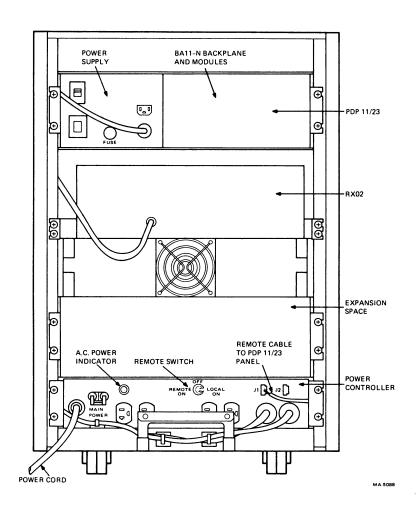

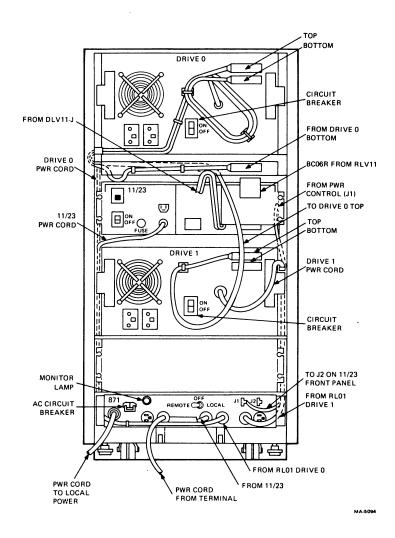

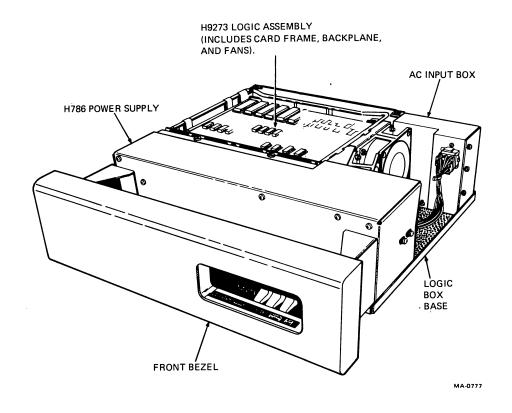

The cabinet for the 11V23 is divided into several major areas. On the top is the 11/23 microcomputer. It is mounted in a BAll-N mounting box with operator's console. Directly below the microcomputer is the RX02 dual floppy disk drive. Unit ZERO is on the left, while unit ONE is on the right. Below the RX02 there is usually a blank panel. In some systems this panel is replaced with a BAll-N expansion chassis. Behind the very bottom panel is the power controller. Figure 2 shows a rear view of the 11V23 system.

Figure 2. PDP-11V23 (Backpanel Removed)

As you view Figures 1 and 2 you will notice that there are a number of controls on the rear of the system as well as on the front. First, let's consider the front panel controls.

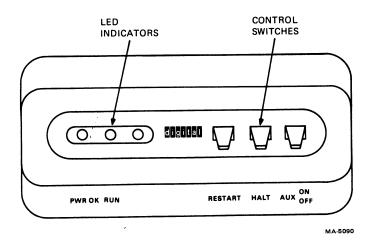

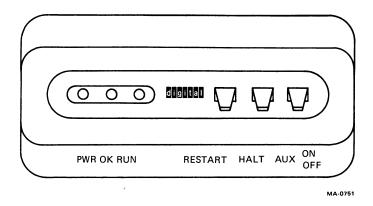

#### Operator's Console

Figure 3 shows the operator's console on the BAll-N. There are three switches and two indicators on the front panel. Table 1 explains the function of each one of these items.

Figure 3. Front Panel Switches and Indicators

Table 1. Control Panel Functions

| Switch/LED    | Position                         | Function                                                                                                                                               |

|---------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUX ON/OFF    | OFF                              | In the normal factory configuration, the ac power is removed from the system.                                                                          |

|               | ON                               | In the normal factory configuration, the ac power is applied to the system. If the HALT switch is up, the system is automatically booted at this time. |

| HALT          | Up (Enable)                      | The processor is enabled to run.                                                                                                                       |

|               | Down (Halt)                      | The processor is halted and will respond to console ODT commands.                                                                                      |

| RESTART       | RESTART<br>(momentary<br>switch) | When the Halt switch is up, the processor carries out a power-up sequence and displays the bootstrap dialogue                                          |

| PWR OK        |                                  | Illuminated when the proper do output voltages are being generated by the microcomputer system.                                                        |

| RUN           |                                  | Illuminated when the processor is operating and is turned OFF when the processor is not executing instructions.                                        |

| (UNMARKED LEI | ))                               | This is a spare indicator which serves no function unless modified by the customer.                                                                    |

#### Rear Panel Controls

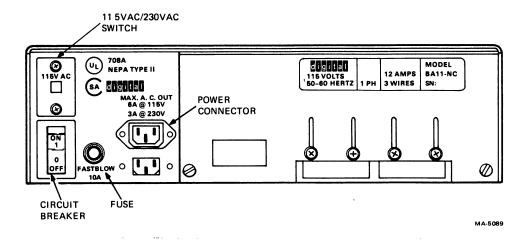

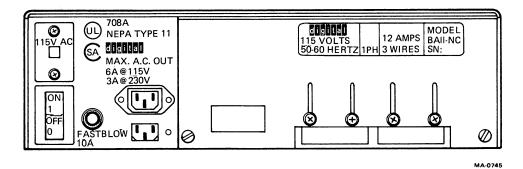

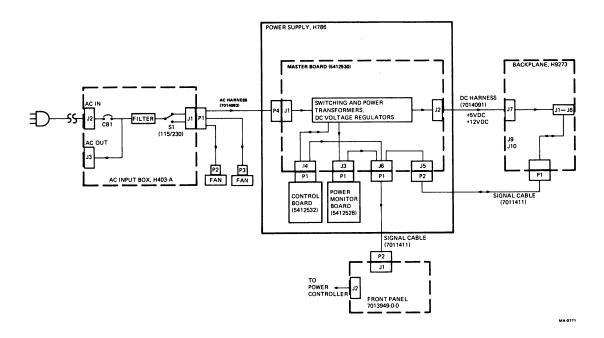

Figure 4 shows a close-up of the rear of the BAll-N mounting box. The circuit breaker on the back of the box also serves as an ON/OFF switch. Primary ac power is supplied through the lower power connector. The upper power connector is usually unused in the 11V23 system. Figure 4 depicts a 115 volt version of the BAll-N.

Figure 4. LSI-11/23 Microcomputer (Rear View)

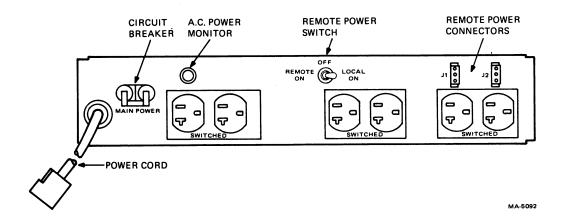

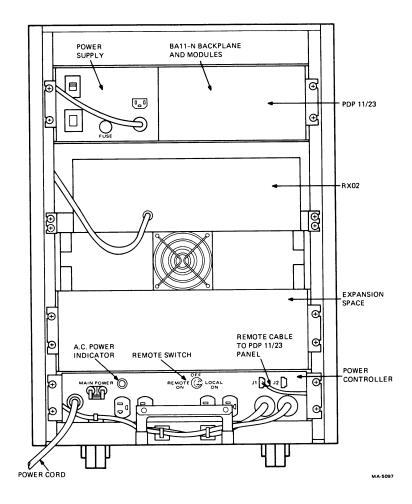

Figure 5 shows the 871 power controller which is mounted at the bottom of the cabinet. The RXØ2 and BAll-N should have their ac power cable plugged into the switched outlet at the far right. The remote cable from the BAll-N should be plugged into Jl. Since the ac power is being remotely controlled from the BAll-N, the remote power switch must be in the REMOTE ON position. Any devices, such as a terminal, which you want to power up or down along with the system should be plugged into one of the switched outlets.

Figure 5. Power Controller (Rear View)

There are three model designations for the 11V23 system. These model numbers depend on power line voltage and frequency. Table 2 summarizes the model designations.

Table 2. PDP-11V23 System Model Designations

| PDP-11V23        | -AA     | -AD     | -AC     |

|------------------|---------|---------|---------|

| Input Voltage    | 115 Vac | 230 Vac | 115 Vac |

| Power Controller | 871-A   | 871-B   | 871-A   |

| Current Rating   | 12 A    | 8 A     | 12 A    |

| Frequency        | 60 Hz   | 50 Hz   | 50 Hz   |

Inspection of the 11V23's specifications which follow shows that the system does not require a special environment. The system can be installed in any typical office or factory floor.

PDP-11V23 Specification Summary

| Environmental Conditions  | Specification                                                                        |

|---------------------------|--------------------------------------------------------------------------------------|

| Altitude                  | 2440 m (8000 ft) maximum                                                             |

| Operating temperature     | 15° to 32° C (59° to 90° F) nominal; reduce temperature 1.8° C/1000 m (1° F/1000 ft) |

| Max. wet bulb temperature | 25° C (77° F)                                                                        |

| Minimum dew point         | 2° C (36° F)                                                                         |

| Storage temperature       | $-40^{\circ}$ C $(-40^{\circ}$ F) to $60^{\circ}$ C $(140^{\circ}$ F)                |

| Temperature change rate   | 11° C (20° F) per hour                                                               |

| Relative humidity         | 10% to 80% (no condensation)                                                         |

| Maximum shock pulse       | 10 gravity peak (half-sine) and $10 \pm 3$ ms duration                               |

| Pitch | and | Roll | +5 | maximum |

|-------|-----|------|----|---------|

|-------|-----|------|----|---------|

#### Power Requirements

| PDP-11V23 System   | 860 W |

|--------------------|-------|

| Optional LA120     | 44Ø W |

| Optional VT100     | 100 W |

| Optional LA34/LA38 | 45 W  |

#### PDP-11T23 SYSTEM OVERVIEW

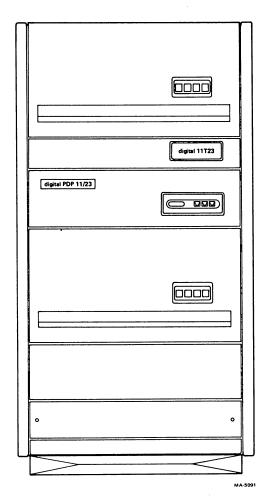

The 11T23 system is similar to the 11V23 with the exception of the fact that in place of the RX02 floppy disk drive there are two RL01 disk drives. Figure 6 shows a typical 11T23 system. From top to bottom, you will find RL01 drive 0, the 11/23 processor, and RL01 drive 1. The disk pack is loaded into drive 0 through a hinged door in the top of the cabinet. To load the disk into drive 1 you must first slide out the disk drive and then place the pack into the top of the drive.

Figure 6. PDP-11T23 System

Figure 7 shows a rear view of the 11T23 system with the rear panel removed. Directly below drive 1 is empty space for a BAll-N expansion box. Below that is the 871 power controller.

Figure 7. PDP-11T23 (Backpanel Removed)

#### RLO1 Disk Drive

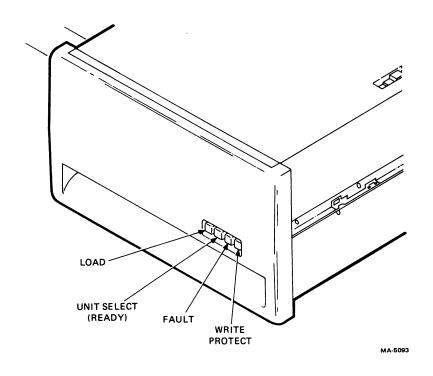

There are a number of controls and indicators on the front panel of the RLØl disk drive (Figure 8). Table 3 gives the function of each of these switches and indicators.

Figure 8. RLØl Disk Drive (Front View)

Table 3. RLØ1 Front Panel Operation

| Indicator                | Function                                                                                             |

|--------------------------|------------------------------------------------------------------------------------------------------|

| LOAD<br>(push-button)    | Lights to indicate that the spindle has stopped and a cartridge can be loaded.                       |

| UNIT SELECT (READY)      | Lights to indicate that drive Ø or l is ready to read, write, or receive controller commands.        |

| FAULT                    | Lights to indicate that a drive error condition exists.                                              |

| WRITE PROT (push-button) | Lights to indicate that the cartridge currently mounted is protected from having data written on it. |

#### PDP-11T23 Specification Summary

The specifications for the 11T23 system are as follows:

Environmental Conditions Specifications

Altitude 2440 m (8000 ft) max

Operating temperature  $10^{\circ}$  to  $40^{\circ}$  C  $(50^{\circ}$  to  $105^{\circ}$  F)

nominal;

reduce temperature 1.8° C/1000 m

(1 F/1000 ft)

Maximum wet bulb temperature  $28^{\circ}$  C  $(82^{\circ}$  F)

Minimum dew point  $2^{\circ}$  C  $(36^{\circ}$  F)

Storage temperature  $-40^{\circ}$  C  $(-40^{\circ}$  F) to  $60^{\circ}$  C  $(140^{\circ}$  F)

Temperature change rate  $16.6^{\circ}$  C  $(30^{\circ}$  F) per hour

Relative humidity 10% to 90% (no condensation)

Maximum shock pulse 10 gravity peak (half-sine) and 10

+ 3 ms duration

Pitch and roll +5 maximum

Power requirements

PDP-11T23 system

860 W

Optional LA120

440 W

Optional VT100

100 W

Optional LA38

45 W

#### PDP-11V23/11T23 OPTIONS

There are many options available with the 11V23/11T23. The modules summarized below are part of a minimum system.

#### Processor

The KDF11-AA is a 16-bit, high-performance microprocessor contained on one dual-height multilayer module (M8186). Utilizing the latest MOS/LSI technology, the KDF11-AA brings the full PDP-11/34 functionality to a microprocessor that communicates along the LSI-11 bus. The KDF11-AA contains memory management as a standard feature and offers floating point as an option (KDF11-A).

The processor uses the LSI-11 bus with new four-level interrupt bus protocol and parity check features. The KDF11-AA is compatible with existing LSI-11 processors and devices.

#### MSV11-D Memory

The MSV11-D module has either 8K, 16K, or 32K by 16 bits of MOS memory. The MSV11-E is the same as the MSV11-D except that it has an 18-bit word that generates and detects byte parity for each word. The modules have on-board memory refresh and perform the necessary LSI-11 bus cycles. The memory addressing is selectable by the user by configuring switch settings. The module can use a battery backup system to preserve data when primary power is lost.

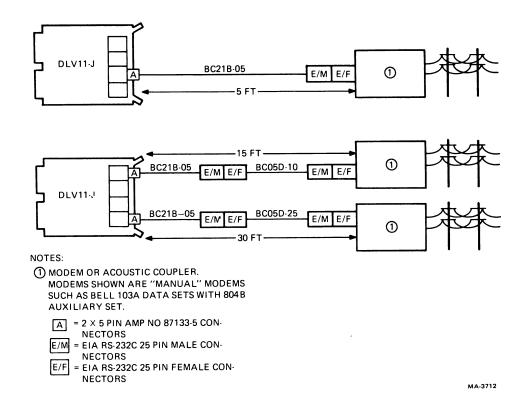

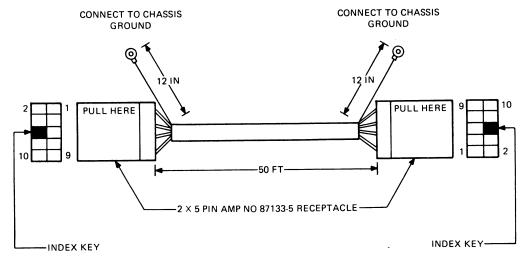

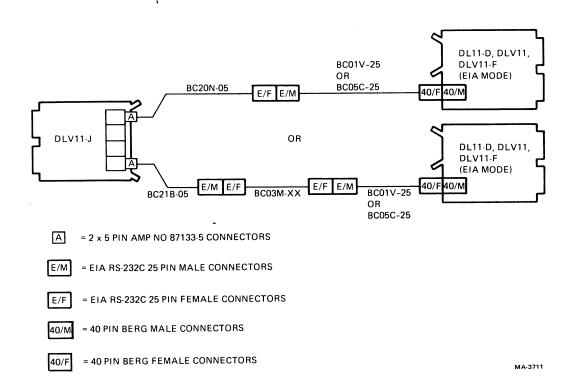

#### DLV11-J Serial Line Unit

The DLV11-J contains four independent asynchronous serial line channels used to interface peripheral devices to the LSI-11 bus. Each channel transmits and receives data from the peripheral device over EIA data leads (lines that do not use a control line). The module can be used with 20 mA current loop devices if a DUV11-KA adapter is used. The DLV11-J has jumper-selectable baud rates from 150 to 38.4K baud.

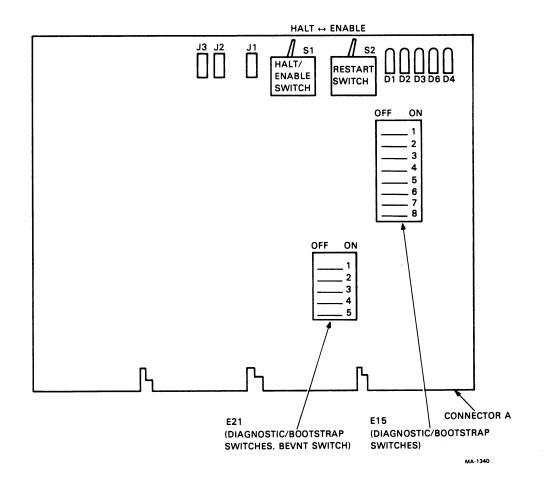

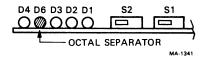

#### BDV11 Bootstrap/Terminator

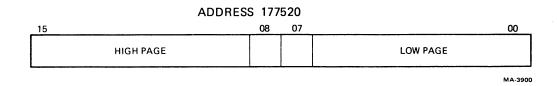

The BDV11 module has 2K words of read-only memory (ROM) that contains diagnostic and bootstrap programs. These programs are user-selectable by setting dual in-line package (DIP) switches. The diagnostic programs will test the processor, the memory, and the user's console. The bootstrap programs can boot LSI-11 peripheral devices. The module also has 120-ohm bus termination circuits.

The user can add up to 16K words of ROM and up to 2K words of erasable programmable ROM (EPROM) on the module. This 18K words of additional memory can be used with no increase in the amount of I/O address space.

#### RXV21 Dual Floppy Disk System

The RXV21 option consists of an interface module, cable assembly, and either a single or dual drive RXØ2 floppy disk. This option is a random access mass storage device that stores data in fixed-length blocks on a preformatted flexible diskette. Each diskette can store and retrieve up to 512K 8-bit bytes of data. The RXV21 system is rack-mountable in the standard 48.3 cm (19 in) cabinet.

This completes the course module for the 11V23/11T23 Introduction. Review the material covered and when you are ready, ask the Course Administrator for the module test.

# PDP-11V23/11T23 SYSTEM MAINTENANCE LSI-11/23 BUS CONCEPTS

## LSI-11/23 Bus Concepts

#### INTRODUCTION

An LSI-11 computer is composed of many different units that operate together to form a complete computer system. These units could include the PDP-11/23 Central Processing Unit (CPU), a semiconductor memory, and any number of peripheral devices, such as a DECscope video terminal, an RXØ2 floppy disk drive, and DECprinter line printer. Operation of the computer system involves transferring addresses, data, and control information among these major system elements.

- 1. Identify the major functions of:

- a bus

- an interface

- 2. Describe the fundamental concepts of the LSI-11 bus by answering test questions on:

- Master/slave relationship

- Dynamic bus control

- Interlocked communication

- 3. Describe the principles of LSI-11 bus cycles by using bus cycle sequence diagrams to answer test questions about the DATI, DATO, DATOB, DATIO, and DATIOB bus cycles.

- 4. Describe the concepts of data transfers by answering test questions on:

- Programmed data transfer

- Interrupts

- Direct Memory Access

Identify the basic principles of LSI-11/23 bus priority by correctly answering questions.

- 5. Describe the principles of the special bus functions by answering test questions about:

- Bus initialization

- Halt mode

- Power-up/power-down sequence

### SAMPLE TEST ITEMS

- 1. Buses carry what type of information?

- a. data only

- b. addresses only

- c. control information only

- d. all the above

- 2. A floppy disk can assume the role of bus master and of bus slave.

True False

- On a DATI bus cycle, the signal BRPLYL is sent in response to:

- a. BDAL 0-15

- b. BDINL

- c. BBS7L

- d. BSYNCL

You may use a bus sequence diagram to answer this question.

- 4. During an interrupt, the CPU sends BIAKOL to the interrupting device in response to what signal?

- a. BSYNCL

- b. BRPLYL

- c. BIROL

- d. BBS7L

- 5. In the halt mode the CPU can still grant interrupts.

| True  |  |

|-------|--|

| False |  |

#### BUS IDENTIFICATION

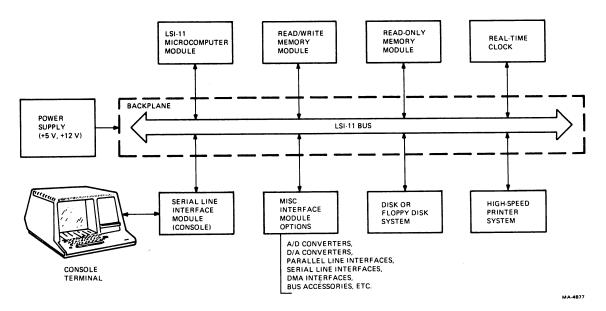

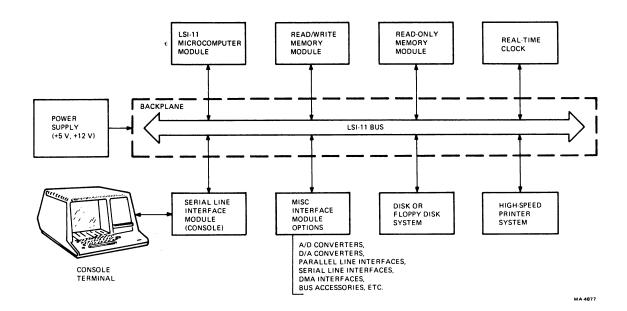

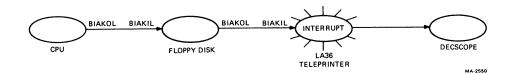

Connections among the CPU, memory, and peripheral devices are made by electric conductors called buses. The conductors that form these buses can be electric cables, etches on a printed circuit board, or even the backplane into which the printed circuit boards are plugged. Buses carry address, data, and control information among the CPU, memory, and peripheral devices. The bus that we will be discussing during this module is the LSI-ll as it is used with the KDF11 processor. Figure 1 shows the LSI-ll bus connecting some typical peripheral devices with the microcomputer module.

Unfortunately, peripherals cannot be simply plugged into Most peripherals are standard devices that have been designed for use with more than one series of computer. For example, the DECscope video terminal is intended to operate not only with the LSI-ll microcomputer but also with any of the PDP-11 minicomputers, the VAX 11/780, and the Because each of these computers much larger DECSYSTEM 20. has its own method of handling data, there must be some method of connecting a peripheral to a specific computer so that the two devices can operate properly. This connection is accomplished by using an interface. An interface may be thought of as a converter placed between a peripheral and a specific computer. All connections from the computer system to the peripheral are made through this interface. see in Figure 1 that the DECscope console terminal connected to the LSI-11 bus by a serial line interface. This interface converts the serial data required by the terminal to a form which can be used by the LSI-11 bus.

Figure 1. LSI-11 Bus Connections

#### EXERCISE

Circle the letter corresponding to the answer which best completes the given statement. You may use references. Check your answers with those given on the next page.

- 1. The conductors that make up a bus can be:

- a. electric cables

- b. etches on a printed circuit board

- c. part of a backplane

- d. all the above

- 2. An interface:

- a. converts serial data to parallel data

- b. converts parallel data to serial data

- c. converts data generated by a device, such as a DECscope, to a form which can be used by the LSI-11 bus

- d. is only required by larger systems such as the VAX 11/780 or the DECSYSTEM 20

# SOLUTIONS

- 1. d

- 2. c

#### **BUS BASICS**

# Master/Slave Relationship

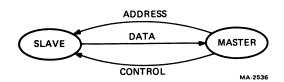

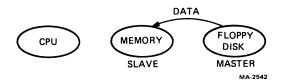

Whenever two devices use the LSI-11 bus to communicate, a master/slave relationship exists. Only two devices can communicate by means of the bus at any given time. When communicating, one device assumes the role of bus master while the other device becomes its bus slave (Figure 2).

Figure 2. Master and Slave

When a bus device becomes a master, its first job is to select the slave that it wants to communicate with. The master selects the slave by placing the address of the desired memory location or I/O device on the LSI-ll bus (Figure 3).

Figure 3. Master selects slave by sending address.

The next job of the master device is to specify the type of operation to be performed. This operation may involve some type of data transfer. By placing control information on the bus, the master specifies the type of operation (Figure 4).

Figure 4. Master specifies type of transfer with control signals.

The master is now ready to initiate a data transfer. Suppose that data must be stored in the selected slave device. In this case the master places data on the bus so that it can be accepted by the slave for storage. Figure 5 shows a bus master sending data to a bus slave.

Figure 5. Master sends data to slave.

The master can also retrieve data from the slave as shown in Figure 6. Although it is now the slave that is putting the data on the bus, the transfer is still controlled by the master. It is the job of the bus master to select the location within the slave from which the data is to be transferred.

Figure 6. Master retrieves data from slave.

As an example, let us say that the CPU bus master wishes to read data from a memory location that is the bus slave. The CPU controls the transfer by addressing the memory and asking for data. The memory responds by sending data. Figures 5 and 6 show that regardless of the direction of the data transfer (master to slave or slave to master), the master always initiates the data transfer and always addresses the slave. A slave can never initiate a data transfer or address another device.

The program being executed by the CPU controls the master/slave relationship. For example, when an RLØl disk acts as bus master and transfers data to memory that is acting as a slave, the program has caused the data transfer to take place. The program has determined who will be master and who will be slave.

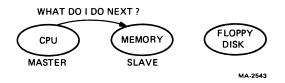

### Dynamic Bus Control

When the program determines that data is to be transferred from the disk to memory, the CPU becomes master and commands the disk to send data. After receiving the command, the disk becomes bus master and sends data to memory, the slave.

Notice how the CPU and peripheral devices can change roles. This change of roles tells us that bus control is dynamic. Dynamic bus control simply means that once a bus master has completed its task, it can pass control of the LSI-ll bus over to another device which then assumes the role of master.

Memory is a slave. It cannot initiate a data transfer or address another device. As shown in Figure 7, the floppy disk system may address the read/write memory. However, the memory can never address the floppy.

Figure 7. Typical LSI-ll System

Let's look at an example to illustrate what is meant by dynamic bus control and how bus mastership changes from one device to another. The system shown in Figure 8 consists of a CPU, a memory, and an RXØ2 floppy disk system. The CPU as master selects the floppy disk to function as slave. It then sends a command to the disk to transfer data to memory.

Figure 8. First the CPU is master.

The CPU gives up control of the bus to the floppy disk (Figure 9). At this point the floppy selects memory as its slave so that it can begin transferring data to memory. Note that the disk retains control of the bus only long enough to transfer its data. Then the disk relinquishes bus control to the CPU or to another device requesting the bus.

Figure 9. Next the floppy disk is master.

At this point, provided another device has not taken control of the bus, the floppy disk informs the CPU that the data transfer to memory is complete (Figure 10). The CPU now becomes bus master, selects memory as its slave, and retrieves an instruction to determine what operation the CPU is to perform next (Figure 11).

Figure 10. The floppy disk tells the CPU that it is finished.

Figure 11. The CPU becomes master once again.

Notice how control of the bus in the example changes back and forth between the CPU and floppy disk. This is what dynamic (constantly changing) bus control means. Also notice that only the CPU and floppy disk assume roles as master since memory is always a slave.

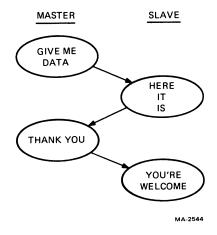

#### Interlocked Communication

Communication between master and slave is interlocked, meaning that no data transfer occurs unless the slave issues a response signal for every control signal sent by the master. If we could listen to a typical dialogue between master and slave where the master wishes to retrieve data from memory, it might sound like this:

Master: Give me data.

Slave: Here it is.

Master: Thank you.

Slave: You are welcome.

Figure 12 is a sequence diagram showing the same dialogue in picture form. You will be referencing sequence diagrams in later chapters to illustrate the relationships among LSI-11 bus signals. For every statement made by the master there is a response from the slave. Now suppose that when the master says, "Give me data," there is no reply from the slave. In this case, all communication with the slave is broken off and the bus is now available for any other device to become master.

Figure 12. Dialogue Between Master and Slave

Because communication is interlocked, the LSI-11 bus is asynchronous. An asynchronous bus can handle devices with a wide range of operating speeds. Each device is allowed to transfer data at its own maximum speed. The DECscope video terminal and the RLØl disk both have very different operating speeds, yet the LSI-11 bus can handle both of them. Interlocked communication allows the LSI-11 bus to be asynchronous. The speed with which the slave replies to the master is unimportant as long as there is a reply.

Field service engineers sometimes refer to interlocked communication as "handshaking," indicating that two devices are present and interacting. The terms "interlocked communication" and "handshaking" have the same meaning and may be interchanged.

#### Summary

In this section we have covered three main points.

- Two devices communicate by means of a master/slave relationship in which the master always controls the bus.

- 2. Bus control is dynamic. It can be passed from one device to another, allowing different devices to assume the role of master.

- All dialogue between the master and slave is interlocked. When the master issues a control signal, the slave must produce a response signal or communication stops.

## EXERCISE

Indicate whether the following statements are true or false by checking either column. You may use references. Check your answers with those given on the next page.

|    |                                                                                                                                                                              | True | False |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| 1. | Whenever two devices use the LSI-ll bus to communicate, a master/slave relationship exists.                                                                                  |      |       |

| 2. | An RLØl can assume the role of bus master as well as that of bus slave.                                                                                                      | -    |       |

| 3. | Memory may address another device and initiate a data transfer.                                                                                                              |      |       |

| 4. | Devices are not built to be bus masters or bus slaves.                                                                                                                       | -    | ·     |

| 5. | The CPU can never become a bus slave.                                                                                                                                        |      |       |

| 6. | Interlocked communication means that if the slave does not issue a response signal for every control signal sent by the master, the master will attempt to remedy the error. |      |       |

# SOLUTIONS

- 1. True

- 2. True

- 3. False

- 4. True

- 5. False

- 6. False

#### BUS CYCLES

### Types of Bus Cycles

In the Introduction you learned that the purpose of the LSI-11 bus is to carry address, data, and control information among the CPU, memory, and peripheral devices. The last section demonstrated how a device becomes bus master, selects a bus slave, and causes a data transfer to take place. Now we will look in detail at the process of data transfer.

There are five types of data transfers or bus cycles that can take place on the LSI-ll bus. In each of the descriptions that follow, the direction of the data transfer is always in relation to that of the bus master.

- DATI During a Data In bus cycle a data word moves from the slave to the master.

- DATO During a Data Out bus cycle a data word moves from the master to the slave.

- DATOB A Data Out Byte bus cycle is similar to a Data Out bus cycle except that here only one byte of data moves from the master to the slave.

- DATIO A Data In-Out bus cycle is a combination of a Data In and a Data Out bus cycle.

First a data word moves from the slave to the master. Then another data word moves from the master to the slave.

- DATIOB A Data In-Out Byte bus cycle is similar

to a Data In-Out bus cycle except that

after a data word is transferred from

the slave to the master, only a byte of

data is returned to the slave.

Before we continue, here are the correct pronounciations for the names of the bus cycles.

DATI is pronounced DATA EYE

DATO is pronounced DATA OH

DATOB is pronounced DATA OH BE

DATIO is pronounced DATA EYE OH

DATIOB is pronounced DATA EYE OH BE

At this point you are ready to study a bus cycle in detail. This study includes a description of what events take place on the bus as well as what bus signals cause these events to take place. All bus signal names are prefixed with the letter B. This letter simply stands for the word "bus." For example BDIN means "bus data in."

All LSI-II bus signals, with the exception of two, have the letter L as a suffix. This letter stands for the word low and means that the signal is at the lower of two logic voltages when true (asserted) and at the higher of two logic voltages when false (not asserted). For example BDINL tells us that the signal BDIN is low when asserted. The two exceptions mentioned earlier are BDCOK H and BPOK H. These two signals are high when asserted.

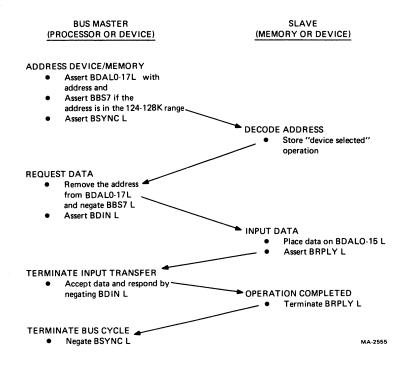

## The DATI Bus Cycle

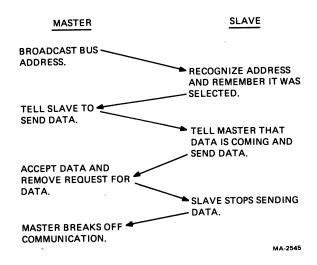

Figure 13 shows a simplified sequence diagram of the events that must take place during a DATI bus cycle. In following the diagram in Figure 13 from top to bottom, notice that the master selects the slave with which it will communicate by broadcasting the address of the slave to every device on the bus. Only the addressed slave recognizes its address and the slave remembers or stores the fact that it has been selected.

Figure 13. Simplified Diagram of DATI Bus Cycle

The master then tells the slave to send data. The slave warns the master that data is coming and then sends a single data word. The master accepts the data word and removes the request for data. When the slave sees that there is no longer a request for data, it stops sending. At this point the master breaks off communication with the slave. The sequence diagram shows not only what events take place but also the order and cause.

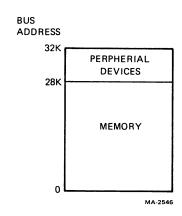

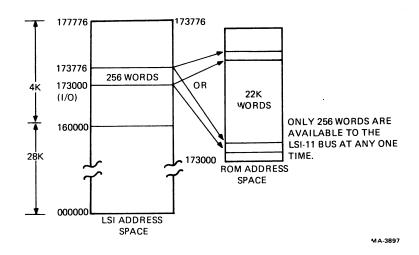

Before looking at a sequence diagram showing the actual bus signals for a DATI bus cycle you must know something about the LSI-11 memory organization. Without memory management the LSI-ll is capable of addressing bus locations from zero all the way up to 32K (32 thousand). Only the first 28K locations can be used for memory. The last 4K locations, 28K to 32K, are reserved for peripheral device interfaces. In short, to address a peripheral device, the bus address must be between 28K and 32K. To address a memory location the bus address must be below 28K. Figure 14 shows memory organization. With memory management the processor is capable of addressing memory up to 124K and a peripheral device address space from 124K to 128K. management will be discussed in detail later in this module.

Figure 14. LSI-ll Memory Organization

The actual sequence diagram shown in Figure 15 recalls the fact that the first thing the master must do is select the slave with which it will communicate by broadcasting the slave's address on the bus.

-- NOTE ---

Throughout the discussion on bus cycles memory management will not be covered.

Figure 15. DATI Bus Cycle

This broadcasting is accomplished on 18 lines referred to as BDALØL through BDAL17L. Remember that the B stands for bus and the L stands for low asserted. The remaining letters, DAL, stand for data and address lines. Thus the 18 lines, BDALØL through BDAL17L, serve two purposes. They can carry an 18 bit bus address or they can carry a 16 bit data word. Without memory management the largest address sent is 16 bits. These lines are also bidirectional, that is, they can carry data or addresses in either direction along the bus.

If a peripheral device is being addressed, that is, if the bus address is between 28K and 32K, the signal BBS7L (bus bank select 7 low) must also be asserted. If we are addressing memory, which has a bus address of less than 28K, then BBS7L is not asserted.

Finally, the master asserts BSYNCL (bus sync low) to inform all devices that an address has been placed on the BDAL lines. BSYNCL remains asserted throughout the bus cycle. The bus master has just completed selection of the slave.

Follow the arrow in Figure 15 to the right. Notice that the selected slave recognizes its address and stores "device selected." Moving back to the left, we can see that the master is now ready to request data. But first it removes the address from DBALØL through BDAL15L and negates (removes) BBS7L. The master now says, "Give me data," by asserting BDINL (bus data in low). The slave, in turn, places the 16 bit data word on lines BDALØL through BDAL15L and says, "Here it is," by asserting BRPLY (bus reply low).

The master accepts the data and signals to the slave that it has the data by negating BDINL. The slave then removes the data from BDALØ-15 and negates BRPLYL. Finally, the master ends the bus cycle by negating BSYNCL.

The sequence diagram we have just looked at assumes normal operation. But, what if the addressed slave is malfunctioning and does not answer? The bus master is looking at the address lines (BDALØ-15L) and at the reply line (BRPLYL). When an address is placed on the bus and there is no reply within 10 microseconds (10 millionths of one second), the CPU ends the bus cycle and begins to execute a program that tries to clear up the problem. If a device other than the CPU is master and there is no reply within 10 microseconds, the device interrupts the operation of the CPU and inform it that an error has taken place.

So far we have looked at 20 of the LSI-ll bus lines:

- BDALØL through BDAL15L

- BBS7L

- BSYNCL

- BDINL

- BRPLYL

Before continuing with this section, look up each of these bus signals in Appendix A and read the corresponding entry. Then return to this point and continue.

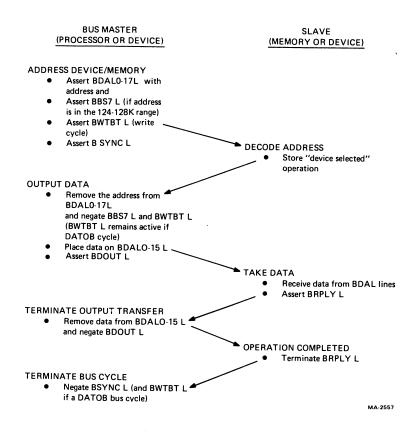

### The DATO and DATOB Bus Cycles

The DATO and DATOB bus cycles (Figure 16) are identical to each other with one exception. The DATO moves a 16 bit data word from the master to the slave, while a DATOB moves an eight bit byte from the master to the slave.

If we look at the top of Figure 16, we can see that the bus cycle starts off in the same way as the DATI bus cycle.

Figure 16. DATO or DATOB Bus Cycle

However, in this case, the master not only selects the slave but also asserts a signal called BWTBTL (bus write byte low). It asserts this signal during the first portion of the bus cycle to tell the peripheral device that we are going to write data. If BWTBTL remains asserted during the last portion of the bus cycle, a byte transfer takes place (DATOB). On the other hand, if BWTBTL is negated during the last portion of the bus cycle, word transfer takes place (DATO).

In the sequence diagram, when the slave recognizes its bus address, it stores "device selected." At this point, the master removes the address from BDALØ-15 and negates BBS7L if it has been asserted. If this is a DATOB bus cycle, then BWTBTL remains active; otherwise, it is negated. Also the master places the data on BDALØ-15 and warns the slave that data is there by asserting BDOUTL (bus data out low).

The slave accepts the data from BDAL0-15 and tells the master it has done so by asserting BRPLYL. When the master sees BRPLYL, it knows that the data has been accepted. It now removes the data from BDAL0-15 and negates BDOUTL.

The slave negates BRPLYL and the master, in turn, negates BSYNCL. The master negates BWTBTL if this is a DATOB bus cycle. In the DATO/DATOB bus cycle, just as in the DATI bus cycle, if BRPLYL is not returned within 10 microseconds from the time an address is placed on BDAL0-15L, the master steps in and ends the bus cycle.

We have just discussed two new signals: BWTBTL and BDOUTL. Before continuing with this section, look up each of these bus signals in Appendix A (p. BC-51) and read the corresponding entry. Then return to this point and continue reading.

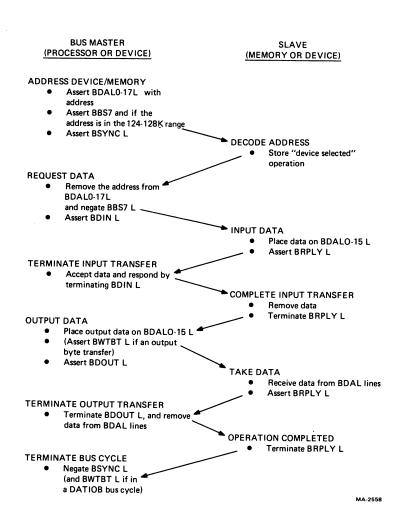

## The DATIO and DATIOB Bus Cycle

DATIO and DATIOB bus cycles can be considered read/modify/write operations. Read/modify/write operations are used whenever data is written back to the same location that it was read from. It takes less time to do a DATIO bus cycle than to do a DATI followed by a DATO bus cycle. First the master reads a data word from the slave (DATI). The master then writes back either a data word (DATO) or a data byte (DATOB) to the slave.

In looking at Figure 17 you can see that the top half of the sequence diagram is identical to the DATI bus cycle. Locate the third entry down under the column headed "Slave." It says "complete input transfer: remove data; terminate BRPLYL." We would expect that the master would now negate BSYNCL, but it does not. Rather, the master begins a DATO or a DATOB bus cycle. Note that the master does not have to put the device address on the bus a second time. It simply goes ahead and places the data on the BDAL lines and sends BDOUTL. Also notice that the signal BWTBTL is only used for the DATIOB bus cycle and not used at all for the DATIO bus cycle.

Figure 17. DATIO or DATIOB Bus Cycle

# Summary

You have just learned about the five types of bus cycles and how they are used to transfer data between the master and slave.

- DATI

- DATO

- DATOB

- DATIO

- DATIOB

We have also looked at the following bus signals and how they are used on the LSI-ll bus.

- BDALØ-17

- BBS7L

- BSYNCL

- BDINL

- BRPLYL

- BDOUTL

- BWTBTL

-

# EXERCISE

| evei         | cycle | e. i | elow are events that take place during a DATI Put them in order by writing the letter of the o the correct number. You may use references. Is wers with those given on the following page. |

|--------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            |       | a.   | Tell master that data is coming and send data.                                                                                                                                             |

| 2.           |       | b.   | Broadcast bus address.                                                                                                                                                                     |

| 3            |       | C.   | Slave removes data from bus.                                                                                                                                                               |

| 4.           |       | đ.   | Accept data and remove request for data.                                                                                                                                                   |

| 5 <b>.</b> _ |       | е.   | Master breaks off communication.                                                                                                                                                           |

6. \_\_\_ f. Tell slave to send data.

# SOLUTIONS

- 1. b

- 2. f

- 3. a

- 4. d

- 5. c

- 6. e

#### DATA TRANSFERS AND PRIORITY

### Methods of Data Transfers

You have learned that the function of the LSI-11 bus is to carry data, addresses, and control information between master and slave devices. Also you have seen that the master uses one of five basic bus cycles to communicate with the slave. In an actual data transfer between a peripheral device and the CPU, the bus master may select one of three methods in which to use these bus cycles to transfer data. They are:

- Programmed data transfer

- Interrupt initiated programmed data transfer

- Direct Memory Access (DMA)

The program being executed by the CPU determines which of the three methods will be used. We will discuss the simplest method first: the programmed data transfer.

### Programmed Data Transfer

To demonstrate programmed data transfer, let's consider a situation where the CPU is to move data from one location to another. This transfer is part of normal program execution of a MOVE instruction.

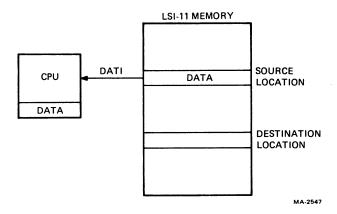

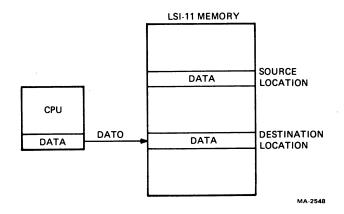

Figure 18 illustrates the LSI-11 memory. The CPU moves data from the source location to the destination location. First the CPU becomes bus master and reads the data in the source location by doing a DATI bus cycle. At the completion of this bus cycle the data has moved to the CPU. Then, as shown in Figure 19, the CPU addresses the destination location and writes the data to memory with a DATO bus cycle.

Figure 18. First the CPU does a DATI bus cycle.

Figure 19. Next the CPU does a DATO bus cycle.

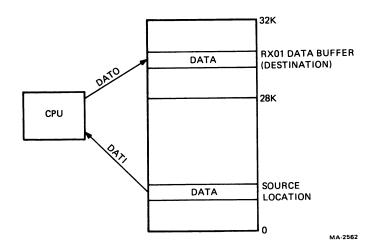

Have you noticed that in this case the CPU has to do two bus cycles to execute the instruction? This instruction cycle requires two bus cycles. If the processor is sending data to a peripheral device, the process is exactly the same. Figure 20 shows the CPU writing data to the RX01 floppy disk memory data buffer.

Figure 20. With a single MOVE instruction, the CPU performs two bus cycles and sends data to the RX01 memory data buffer.

First the CPU retrieves the data by addressing the source location and does a DATI bus cycle. Next the processor sends this data to the RXØl by addressing its data buffer and doing a DATO bus cycle. The only difference between this example and the one shown in Figure 19 is that here the bus address of the destination location is in the top 4K of the address range. Remember that bus addresses between 124K and 128K are reserved for peripheral devices and are not part of memory. These two examples clarify what programmed data transfer involves. When the processor is executing a program and some of the instructions in the program move data to peripheral devices, the CPU is performing a programmed data transfer.

Let's look at some of the features of a programmed data transfer. First, it can only be performed by the CPU because only the CPU can execute instructions. Secondly, a programmed data transfer requires no special bus signals. The CPU simply addresses the device and does a bus cycle. Finally, the addressed device must be ready to transfer data. If it is not ready, the transfer is very slow. In Figure 20, if the RX01 is not ready to accept the data word, the CPU has to stop and wait until the data can be accepted.

### Interrupt Initiated Programmed Data Transfer

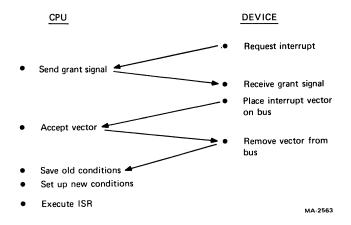

Interrupts allow the CPU to execute a program without being tied up waiting for a device to become ready to transfer data. When the device becomes ready, it interrupts the CPU and says, "I am ready for data." Then the CPU stops executing its program and begins a programmed data transfer between itself and the interrupting device. Figure 21 is a simplified sequence diagram showing the basic events that take place during an interrupt.

Figure 21. A Simplified Interrupt Sequence Diagram

Initially, the device requests an interrupt. The CPU, upon receiving the interrupt request, sends out an interrupt grant signal. Without this signal the interrupting device cannot continue.

The device places a vector address on the bus just as soon as it receives the grant. A vector (or pointer) address tells the CPU where in memory it can find the address of first instruction of a program. The program that this vector is pointing to is called an Interrupt Service Routine (ISR).

Contrary to what some people think, CPUs are not intelligent. When a device interrupts, the CPU has no idea of what to do. So the interrupting device sends over a vector address. This address points to the address of first instruction in the ISR. Once it begins to execute, this program must do two things. First it must find out what the device wants; then it must perform the operation indicated by the interrupting device.

So in our sequence diagram, the device has just put its interrupt vector on the bus. After the CPU accepts this vector the device will remove the address from the bus. As the final operation in servicing the interrupt, the CPU must store the old processor conditions so that it knows where to continue after the interrupt. It loads the new processor conditions so that it knows where to start the ISR. And finally it begins to execute the ISR.

What happens now depends upon the device that is interrupting as well as the reason why it is interrupting. After the ISR determines what the interrupting device wants, it will usually perform one of the five basic bus cycles discussed in the last lesson. Let's say, for example, that the CPU does a DATO and transfers a single word to the device. The operation for which the device interrupted the CPU is now over. The CPU gives up control of the bus and continues with the program it was executing before the interrupt took place.

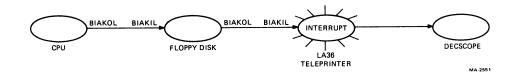

The important thing to remember about an interrupt is that it is a method of attracting the attention of the CPU. Once the processor's attention has been attracted a programmed data transfer takes place. Figure 22 shows an actual interrupt sequence diagram. This diagram contains some new bus signals. You will encounter some signals that have already been discussed, only this time they are used differently.

Figure 22. Interrupt Request/Acknowledge Sequence

Now we will follow the sequence of events as a DECscope video terminal interrupts the processor to send a single data byte. The sequence begins with the DECscope controller requesting an interrupt by asserting BIRQL (bus interrupt request low). The CPU then sends BDINL and the interrupt grant signal BIAKOL (bus interrupt acknowledge out low). The DECscope controller receives the grant signal as BIAKIL (bus interrupt acknowledge in low) and replies by placing the vector address on BDALØ-17L and asserting BRPLYL. (BIAKOL and BIAKIL are two names for the same signal. We will discuss this signal in detail when you learn about bus priority.)

BIRQL can now be negated. The processor accepts the vector address and indicates this acceptance by negating BDINL and BIAKOL. Next the DECscope controller removes the vector address from the bus and negates BRPLYL. Finally the CPU executes the ISR, services the controller, and ultimately returns to its original program.

One question remains about interrupts. When can one take place? An interrupt can only take place after the end of an instruction cycle. This is because the CPU must stop executing its program in order to do the ISR. An instruction in the standard instruction set must always be completed before a new one is started.

You have learned about two new signals from the previous example: BIRQL and BIAKOL/BIAKIL. You have also seen that BDINL is used differently here than it has been in other examples. Before continuing, look up these signals in the table in Appendix A (p. BC-51) and read the corresponding entries. Then return to this point and continue reading.

#### Direct Memory Access

The Direct Memory Access (DMA) is the fastest type of data transfer. During a DMA, a high speed peripheral device, usually a disk, reads or writes data directly to memory without disturbing the processor. Memory is always the slave while the high-speed device is the master.

Before a DMA can take place, there are two registers which must be set up under program control. These are the Word Count Register and the Memory Address Register. When the program being executed by the CPU determines that it is time to transfer data to or from a high speed device, the CPU places the number of words to be transferred in the Word Count Register. Also the address of the first memory location from which data is read from or written to is placed in the Memory Address Register.

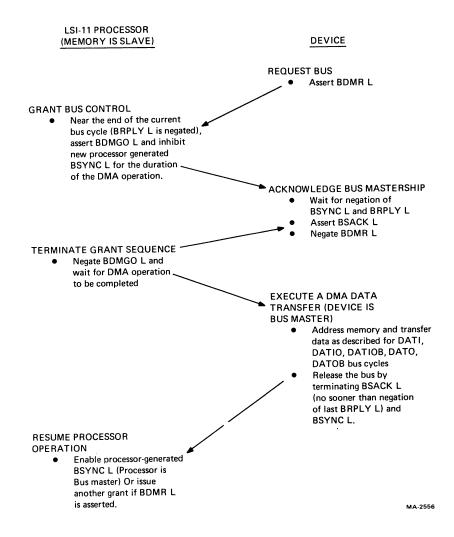

Circuits on the CPU module are used to arbitrate the DMA, that is to decide who will be allowed to do a DMA and when a DMA can be done. The CPU can arbitrate DMAs at the same time it is executing a program. First, this means that the DMA can be arbitrated, or set up, while the bus is still being used by another master/slave pair. At the completion of the present bus cycle, the peripheral breaks in and transfers data. Upon completion of the transfer. Secondly, at the completion of the mastership is given up. bus cycle, the CPU immediately resumes executing its Since the CPU has not been disturbed during the program. DMA, there is no need to restore the contents of any registers as was required after an interrupt. As you look at the simplified DMA sequence diagram shown in Figure 23, notice that the first two steps can take place even if another master/slave pair is using the bus.

Figure 23. Simplified DMA Sequence Diagram

The device requests a DMA and the CPU grants it. Nothing more happens until the bus is free. At the end of the next bus cycle the device becomes bus master. The CPU waits for the DMA to take place. The device can now do any one of the five basic bus cycles and then give up the bus. In the last step the CPU simply resumes operation. Figure 24 shows the actual DMA sequence and the bus lines that are involved in the requesting and granting of the bus.

A device requests the bus by asserting BDMRL (bus DMA request low). The processor responds by sending BDMGOL (bus DMA grant out low), thus allowing the device to become bus master. This signal also stops further processor generation of BSYNCL, preventing the processor from starting a new bus The device receives the grant signal as BDMGIL (bus cycle. As soon as the bus is idle (BSYNCL and DMA grant in low). BRPLYL are both negated), the device takes over as bus master by asserting BSACKL (bus selection acknowledge low). (BDMGOL and At the same time the device negates BDMRL. BDMGIL are two names for the same signal. This signal will be discussed in detail when you learn about bus priority.) The CPU now negates BDMGOL and waits for the DMA to take The device does any one of the five basic bus cycles and then gives up the bus by negating BSACKL. Finally the CPU resumes its normal operation.

Figure 24. DMA Request/Grant Sequence

The most important feature of DMA is that when the CPU arbitrates the request, it does not have to stop executing its program. For this reason, a DMA can be performed between any two bus cycles, even if this means that the DMA falls in the middle of an instruction cycle. Additionally, a DMA can still be arbitrated when the processor is halted. Since the ability to execute a program has nothing to do with the DMA process, the CPU can still service the DMA when halted.

You have learned three new signals: BDMRL, BDMGOL/BDMGIL, and BSACKL. Before reading on, look these signals up in the table in Appendix A and read the corresponding entries. Then return to this point and continue reading.

## LSI-11 Bus Priority

In our discussion of interrupts and DMAs, every time a device requested the bus, the request was always granted. This is because we assumed that the device requesting bus mastership was the only device on the bus. In a real system, this is not the case. A small system may include an LA36 teleprinter, a DECscope video terminal, and an RXØ2 floppy disk. While the CPU module is performing programmed data transfers, the peripherals are attempting to take over bus mastership through interrupts and DMAs.

The CPU must be able to arbitrate these requests for the bus. Through arbitration, the CPU decides which device gets control of the bus. This is done by assigning each device a specific priority. If two or more devices ever request the bus at the same time, the device with the highest priority will always gain control. The KDF11 processor is capable of two methods of bus priority. One method uses a serial priority scheme which is totally compatible with the older 11/03 systems. The second method employs a multi-level priority scheme which is not presently supported by DIGITAL software. The multi-level scheme will be explained here because it may be used on future DIGITAL systems.

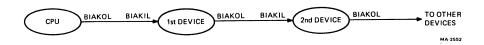

## Serial Priority

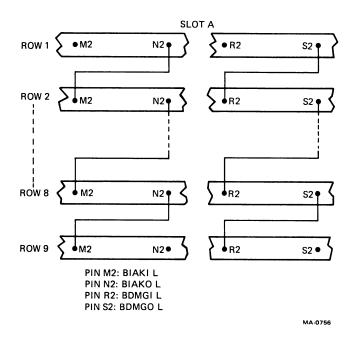

With the exception of priority grant signals, all signals are passed along the LSI-11 bus so that they are received by all devices at the same time. (There actually is a very small delay along the bus, but it can be neglected in a well-designed system.) The priority grant signals are daisy-chained, or transmitted serially along the bus as shown in Figure 25.

Figure 25. The interrupt grant signal is daisy-chained along the LSI-ll bus.

Here we can see that the CPU generates the interrupt grant signal BIAKOL. This signal is serial in the sense that it has to pass through the internal circuits of each device controller before it leaves the other side. Notice how the name of the signal changes as it gets passed from device to device. If the signal is leaving a module, such as the CPU or device controller, it is called BIAKOL (bus interrupt acknowledge OUT low). If the SAME signal is about to enter a module, it is called BIAKIL (bus interrupt acknowledge IN low).

Let's set up some rules for this grant signal. First, if a device requests an interrupt, it must receive BIAKIL asserted to continue with the interrupt. Secondly, if a device requesting an interrupt receives BIAKIL asserted, it will NOT pass the signal on to the next device. Only if the device is not requesting an interrupt will it pass BIAKOL on to the next device. Lastly, a device raises an interrupt by asserting BIRQ4L.

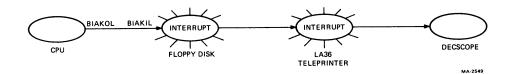

Figure 26 shows a system with three devices on the bus. The LA36, which is requesting the interrupt, captures the grant signal. It has received BIAKIL asserted but does not pass it on to the next device. Note that the floppy disk which is not interrupting passes BIAKIL to the next device.

Figure 26. The LA36 teleprinter captures the grant signal.

What if two devices interrupt at the same time? In looking at Figure 27, we can see that both the floppy disk and the LA36 teleprinter are interrupting. Since the floppy disk has captured the grant signal, the LA36 cannot continue with its interrupt. However, the floppy disk can continue, and when it is finished transferring data, it will pass on the BIAKOL grant signal the next time it is raised. In Figure 28, the LA36 receives BIAKOL and proceeds with its interrupt.

Figure 27. Two devices raise an interrupt at the same time.

Figure 28. The LA36 continues with its interrupt.

Figure 28 demonstrates a very important principle of serial priority. The device closest to the CPU along the LSI-11V23 bus has the highest priority. In other words, if more than one device interrupts at the same time, the device closest to the CPU will always be serviced first.

DMA priority is handled in exactly the same way. Every device that is capable of performing a DMA has the signal BDMGOL/BDMGIL daisy-chained through it. Also a device requests a DMA by asserting the signal BDMRL. Therefore the device closest to the CPU will be granted DMAs before any other device.

# Four-Level Interrupt Scheme

The KDF11 is capable of using a four-level interrupt scheme.

The four-level interrupt scheme is not supported by DIGITAL software.

There are four interrupt request lines on the LSI-ll bus. They are designated BIRQ4L through BIRQ7L. When the KDF11 sees a request on one of these lines it will acknowledge it according to the following rules.

BIRQ7L is considered the highest priority request level, while BIRQ4L is the lowest priority level. This means, for example, that if requests were raised by BIRQ4L and BIRQ6L at the same time, the processor would acknowledge the level 6 request first.

On the other hand, the device interfaces must follow certain rules for asserting and monitoring the request lines. These rules are shown in Table 1.

--- NOTE -

Presently DIGITAL manufactured interfaces only assert BIRQ4L and do not monitor any request lines.

Table 1. Device Interface Request Levels

|                    |                              | D                             |

|--------------------|------------------------------|-------------------------------|

| Interrupt<br>Level | Request<br>Lines<br>Asserted | Request<br>Lines<br>Monitored |

| Level 4            | BIRQ4L                       | BIRQ5L<br>BIRQ6L              |

| Level 5            | BIRQ4L<br>BIRQ5L             | BIRQ6L                        |

| Level 6            | BIRQ4L<br>BIRQ6L             | BIRQ7L                        |

| Level 7            | BIRQ4L<br>BIRQ6L<br>BIRQ7L   | (None)                        |

Lets look at two examples to see how this table is used.

# Example 1:

If a level 7 device requested an interrupt, the following would take place:

- Level 6 devices will not interrupt because they are monitoring level 7.

- Level 5 devices will not interrupt because they are monitoring level 6.

- 3. Level 4 devices will not interrupt because they are monitoring level 6.

Example 2:

If a level 6 device requested an interrupt, the following would take place:

- 1. A level 7 device could still interrupt because it does not monitor request lines.

- 2. Level 4 and 5 devices will not interrupt because they both are monitoring level 6.

This complex system is used for two reasons. It enables older software which only recognizes interrupt level 4 to be used. Also this scheme uses the least amount of ICs on the processor module.

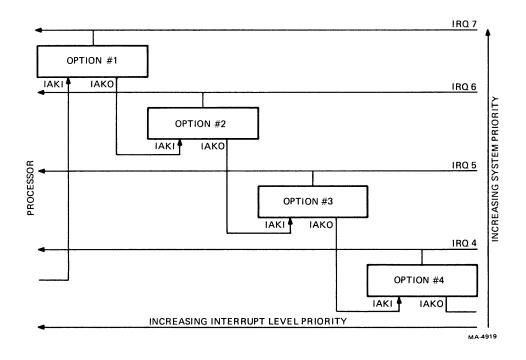

There are two ways to use these request levels. There is a position independent configuration and a position dependent configuration. Figure 29 shows the position dependent configuration. This configuration is similar to the older serial method in that the module closest to the processor has the highest priority. As shown in Figure 29, the device in option location 1 has a higher priority than the device in location 2. This priority level continues all the way down the bus. The position dependent configuration does not limit you to four devices. It is possible to place more than one device on the same request line. Suppose two devices request an interrupt at the same time on level 6.

Figure 29. LSI-11/23 Position Dependent Modules

The device that is physically closer to the processor still has the highest priority. This is because the interrupt acknowledge signal is still daisy-chained through each device.

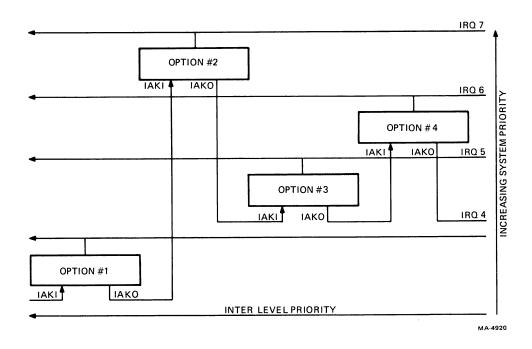

A typical example of a position independent configuration is shown in Figure 30. In this particular example the device in option location 1 (closest to the processor) has the lowest priority because it is connected to request level 4. In this figure the order of priority from highest to lowest is:

- Option 2

- Option 4

- Option 3

- Option 1

As in the previous example, more than one device can be attached to a request level.

Figure 30. LSI-11/23 Position Independent Modules

# Summary

In this section we have discussed three types of data transfers: programmed data transfers, interrupts, and direct memory accesses. These items are compared in Table 2. We have also looked at the LSI-11 bus priority scheme which gives devices closest to the CPU the highest priority.

Table 2. Data Transfers

|                                 | Programmed<br>Data Transfer | Interrupt                       | DMA                               |

|---------------------------------|-----------------------------|---------------------------------|-----------------------------------|

| Speed                           | slowest                     | faster                          | fastest                           |

| Who can<br>perform<br>transfer  | CPU<br>only                 | most devices<br>(except memory) | any DMA<br>(high speed)<br>device |

| When can<br>transfer<br>be done | when CPU<br>becomes master  | between<br>instructions         | between<br>bus cycles             |

| If CPU<br>is<br>halted          | can not be<br>done          | can not be<br>honored           | can still be arbitrated           |

### EXERCISE

Circle the letter corresponding to the correct response for each question/statement. You may use references. Check your answers with those given on the next page.

- During programmed data transfer how many bus cycles can an instruction cycle have?

- a. one

- b. two

- c. more than two

- d. all the above

- 2. When an interrupt request is received by the CPU: the CPU will:

- a. send a grant signal

- b. send a vector address

- c. accept a vector address

- d. execute the ISR

- 3. When the bus master is performing a bus cycle during a DMA, the CPU will:

- a. send a grant signal

- b. wait for the DMA to complete

- c. execute an ISR

- d. continue executing its program

- 4. An interrupting device must wait for the grant signal before continuing with the interrupt.

| Tru | e  |  |

|-----|----|--|

| Fal | se |  |

5. For interrupts, the device closest to the CPU has the highest priority, while for DMAs the device furthest from the CPU has the highest priority.

| Tr | u | e | <b>:</b> |

|----|---|---|----------|

| Fa | 1 | s | e        |

# SOLUTIONS

- 1. d

- 2. a

- 3. b

- 4. True

- 5. False

### SPECIAL BUS FUNCTIONS

# Special Functions

You will now learn about operations that take place on the LSI-ll bus, but are not used for data transfer. These operations are bus initialization, power-up/power-down sequence, and the processor halt mode. You will also learn about the remaining bus lines.

## Bus Initialization

The bus can be initialized in one of two ways: by the CPU executing a RESET instruction or by going through a power-up or power-down sequence. The CPU initializes the bus by asserting the signal BINITL (bus initialize low) for 10 microseconds. This signal is used by devices along the bus to clear registers, reset circuits, and, in some cases, to initiate self test diagnostic programs.

#### Halt Mode

If the bus halt line, BHALTL, is asserted the CPU goes into the halt mode. Even though the CPU cannot execute a program in this mode, it still arbitrates DMAs and executes the microcode ODT. ODT (On-Line Debugging Technique) is the LSI-ll's microcode console emulator.

BHALTL can be asserted by the console Halt switch. The BHALTL line can also be asserted by depressing the BREAK key on the console teleprinter, provided the proper jumpers are in place on the serial line unit.

### Power-Up/Power-Down Sequence

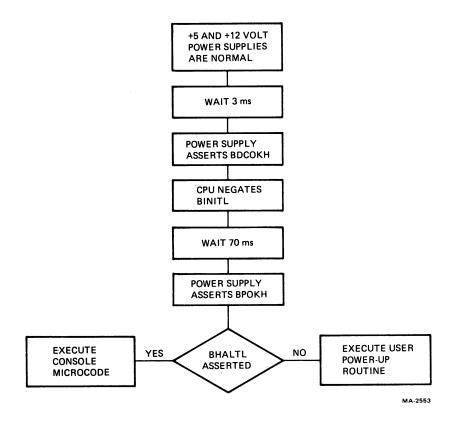

The bus power-up sequence (Figure 31) allows for the automatic starting of a user's program when power is applied to the computer system. The power-down sequence (Figure 32) allows the CPU to execute a program which saves important data in the three milliseconds between the time the power failure is sensed and power supply voltages are lost.

In order to take advantage of the power-up/power-down sequence, the system must include some Read Only Memory (ROM), core memory, or MOS memory with battery backup. If none of these options are present all programs and data stored in memory are lost when power is removed.

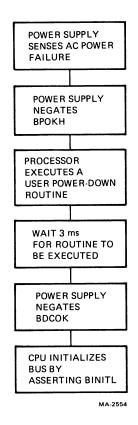

Figure 31. The Power-Up Sequence Flowchart

As Figure 31 shows, when power supply voltages become normal, a three millisecond delay begins. At the end of this delay the power supply asserts BDCOKH (bus DC is OK high). The CPU responds by negating BINITL, which until now was held asserted from the time that power was applied. There is now a second time delay, lasting for 70 milliseconds, at the end of which the power supply asserts BPOKH (bus power OK high). The CPU now examines the BHALTL line. If it is asserted, the CPU executes the ODT microcode. If it is not asserted, a user-supplied power-up routine is started.

When the power supply senses a failure of the ac power, it negates BPOKH. This signals the CPU to execute a user-supplied power-down routine. Three milliseconds after BPOKH is negated, the CPU completes the sequence by asserting BINITL to initialize the bus (Figure 32).

Figure 32. The Power-Down Sequence Flowchart

# Miscellaneous Bus Lines

There are still two have not been signals that refresh first is BREFL (bus explained. The Semiconductor memories that are used with the LSI-ll must be Older-style memories had to be periodically refreshed. refreshed by an external device or by the CPU. BREFL is asserted to start the refresh process. Newer-style memories can perform an internal refresh and no longer use this line. The topic of Memory Refresh will be included in your Systems Course when you learn about semiconductor memories.

The second signal is BEVNTL (bus event low). This signal is used to note the occurrence of a selected event. When BEVNTL is asserted, the processor automatically services this interrupt request through a vector address found in location 100 (octal). No vector address is transferred as happens in the normal interrupt. This line is usually used for the line time clock option which uses the power line frequency (50 or 60 Hz) to measure time intervals.

# EXERCISE

Indicate whether the following statements are true or false by checking either column. You may use references. Check your answers with those given on the next page.

True False

| 1. | Every time a RESET instruction is executed, an initialization pulse is sent down the LSI-ll bus.        | <br> |

|----|---------------------------------------------------------------------------------------------------------|------|

| 2. | After BHALTL is asserted, the CPU can still arbitrate DMAs.                                             | <br> |

| 3. | During a power-up and power-<br>down sequence, the user must<br>supply the routine that is<br>executed. | <br> |

| 4. | The signals BPOKH and BDCOKH are the only two high asserted signals on the LSI-11 bus.                  | <br> |

| 5. | The signal BEVNTL is used to refresh semiconductor memories.                                            |      |

# SOLUTIONS

| 1 |   | т∽ | ue |

|---|---|----|----|

| 1 | • | 11 | ue |

- 2. True

- 3. True

- 4. True

- 5. False

This completes the course module for the LSI-11/23 bus concepts. Review the material covered and when you are ready, ask the Course Administrator for the module test.

# APPENDIX A

# SIMPLIFIED LIST OF LSI-11 BUS SIGNALS

| · |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

| Signal                    | Name                                               | Function                                                                                                              |

|---------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| BDALØL<br>thru<br>BDAL17L |                                                    | These 16 lines carry addresses and data during a portion of the bus cycle.                                            |

| BBS7L                     | Bank 7 Select                                      | The address that is currently on<br>the address lines is between 124K<br>and 128K(11/23)                              |

| BSYNCL                    | Synchronize                                        | Asserted by the bus master to indicate it has put an address on the bus.                                              |

| BDINL                     | Data In                                            | <ol> <li>During a bus cycle, it tells<br/>the slave to send data.</li> </ol>                                          |

|                           | ·                                                  | <ol> <li>During an interrupt, it<br/>signals to all bus devices<br/>that an interrupt is taking<br/>place.</li> </ol> |

| BRPLYL                    | Reply                                              | Asserted by the slave to indicate that it has accepted data or placed data on the bus.                                |

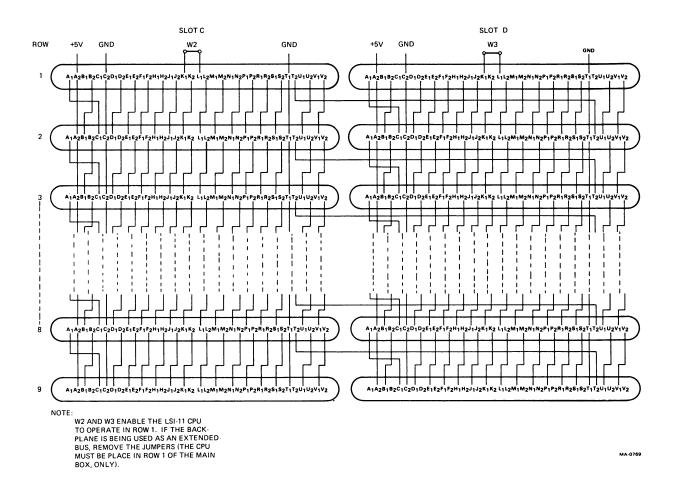

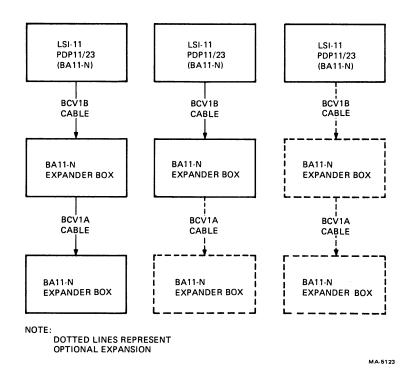

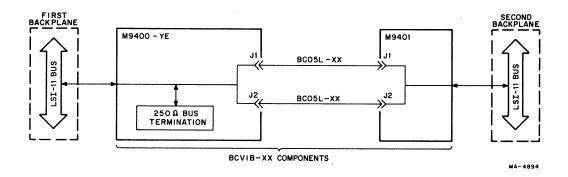

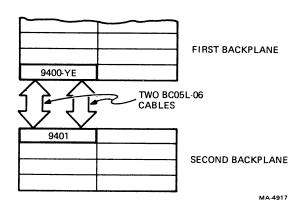

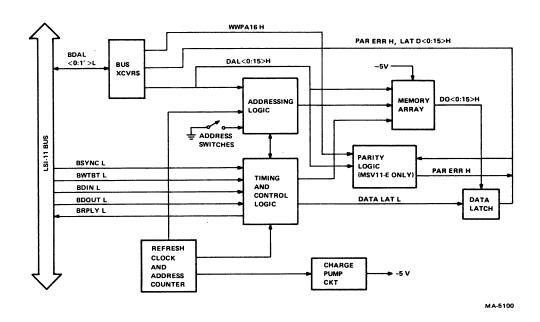

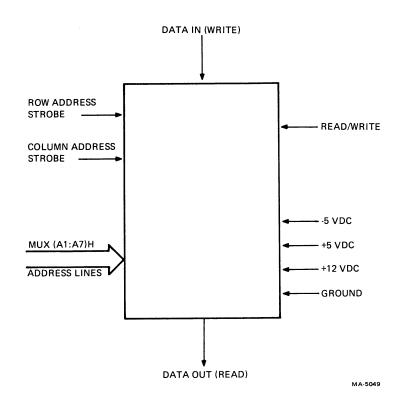

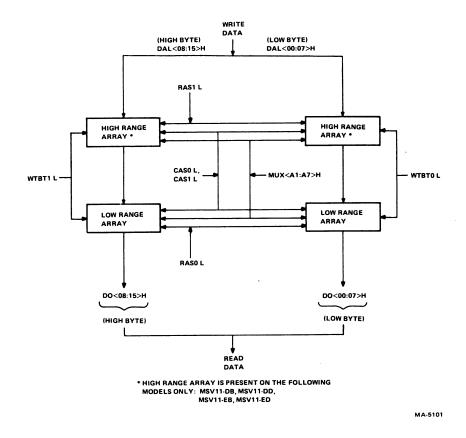

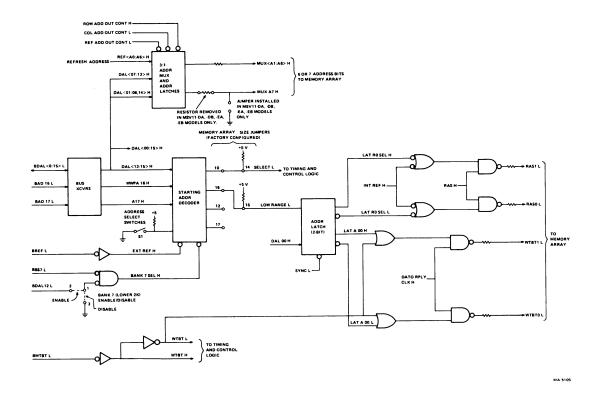

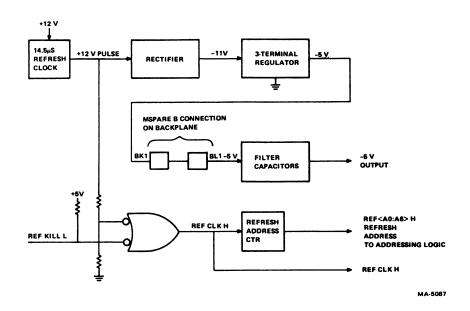

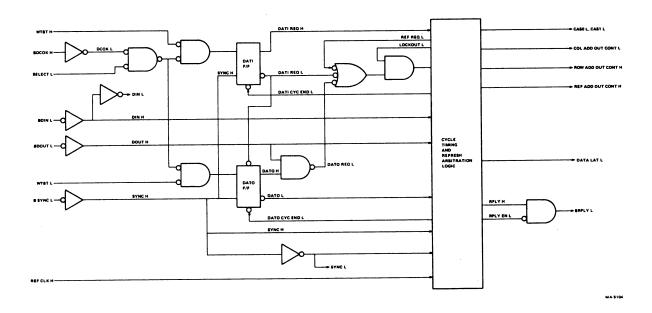

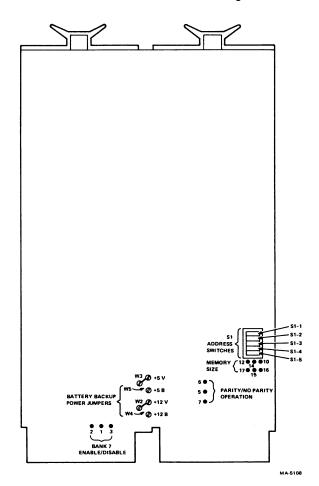

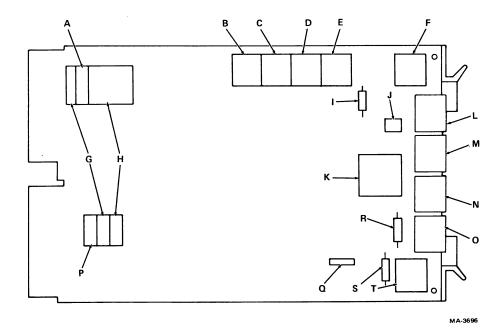

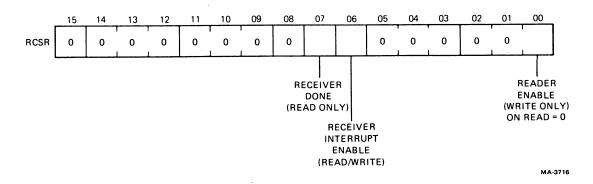

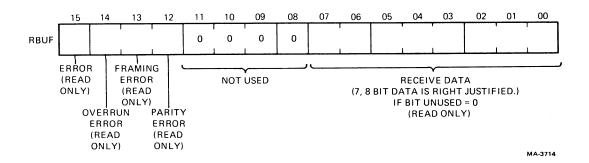

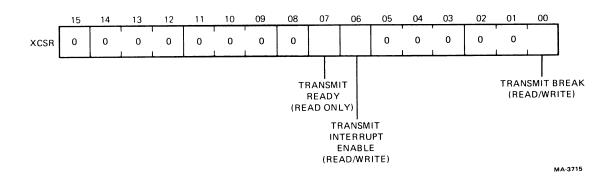

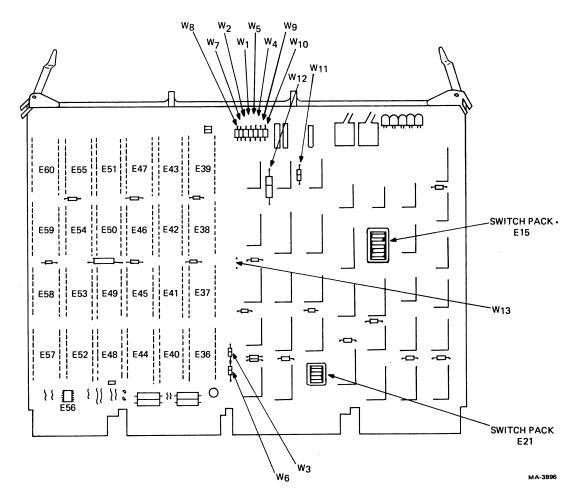

| BDOUTL                    | Data Out                                           | When asserted, tells the slave that data is on the bus.                                                               |